译码器

发布时间:2014/7/12 13:37:24 访问次数:1648

译码器分两大类,一类是通用译码器,另一类是显示译码器,本实验仅介绍前者。

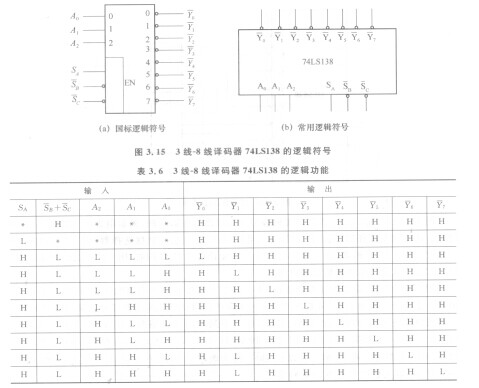

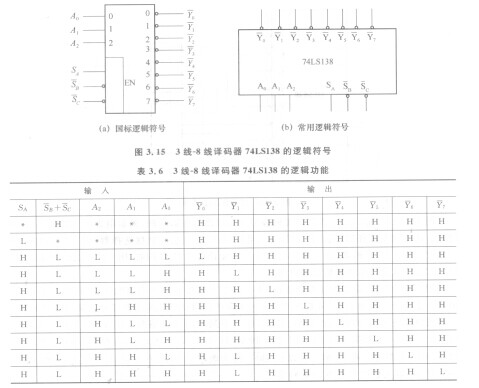

74LS138是3线一8线译码器,XC2064-70PC68C是一种通用译码器,其逻辑符号如图3.15所示,其功能如表3.6所示。其申,A。、A.、A。是地址输入端,y。、Yl、…、y,是译码输出端,SA、S。、亏。是使能端,仅当SA、SB、SC分别为H、L、L时,译码器才正常译码;否则,译码器不实现译码,这时不管译码输入A2、Ai、A。为何值,8个译码输出y。、Yl、…、y,都输出高电平。3线一8线译码器实际上也是一个负脉冲输出的脉冲分配器。如利用使能端中的一个输入端输入数据信息,器件就成为数据分配器。例如,若从SA输入端输人数据信息,SB―SC =0,地址码所对应的输出是SA数据信息的反码;若从SB输入端输入数据信息,SA =1,Sc =0,地址码所对应的输出就是数据信息Sn。 .

译码器的每一路输出,实际上是各地址变量组成函数的一个最小项的反变量,利用其中一部分输出端输出的与非关系,也就是它们相应最小项的或逻辑表达式,能方便地实现逻辑函数。

例如,用3线-8线译码器实现全加器的劝能。设A。和B。分别是被加数和加数,C。是低位向本位的进位,C。+,是本位向高位的进位,S。是和数。全加器的逻辑表达式为Sn =An B,, C,,+AnB,, C,,+An BnCn +AnBnCn= Yi +Y2+Y4+Yr =Y, Y2 Y4 Y7

Cn+.一A.B.C.+A.B.C.+A.B.C.+A.B.C.=Y3+Y5十Y6+Y7=Y3 Y5 Y6 y,上列表达式可用如图3. 16所示的电路来实现。

用MSI组合功能件设计组合电路的基本步骤同用小规模集成电路(SSI)设计的步骤,只是逻辑表达式应该表示成类似于所选用的MSI组合功能件的输出/输入的标准逻辑表达式,以便很方便地应用所选用的MSI组合功能件实现实际问题所要求的逻辑功能。

译码器分两大类,一类是通用译码器,另一类是显示译码器,本实验仅介绍前者。

74LS138是3线一8线译码器,XC2064-70PC68C是一种通用译码器,其逻辑符号如图3.15所示,其功能如表3.6所示。其申,A。、A.、A。是地址输入端,y。、Yl、…、y,是译码输出端,SA、S。、亏。是使能端,仅当SA、SB、SC分别为H、L、L时,译码器才正常译码;否则,译码器不实现译码,这时不管译码输入A2、Ai、A。为何值,8个译码输出y。、Yl、…、y,都输出高电平。3线一8线译码器实际上也是一个负脉冲输出的脉冲分配器。如利用使能端中的一个输入端输入数据信息,器件就成为数据分配器。例如,若从SA输入端输人数据信息,SB―SC =0,地址码所对应的输出是SA数据信息的反码;若从SB输入端输入数据信息,SA =1,Sc =0,地址码所对应的输出就是数据信息Sn。 .

译码器的每一路输出,实际上是各地址变量组成函数的一个最小项的反变量,利用其中一部分输出端输出的与非关系,也就是它们相应最小项的或逻辑表达式,能方便地实现逻辑函数。

例如,用3线-8线译码器实现全加器的劝能。设A。和B。分别是被加数和加数,C。是低位向本位的进位,C。+,是本位向高位的进位,S。是和数。全加器的逻辑表达式为Sn =An B,, C,,+AnB,, C,,+An BnCn +AnBnCn= Yi +Y2+Y4+Yr =Y, Y2 Y4 Y7

Cn+.一A.B.C.+A.B.C.+A.B.C.+A.B.C.=Y3+Y5十Y6+Y7=Y3 Y5 Y6 y,上列表达式可用如图3. 16所示的电路来实现。

用MSI组合功能件设计组合电路的基本步骤同用小规模集成电路(SSI)设计的步骤,只是逻辑表达式应该表示成类似于所选用的MSI组合功能件的输出/输入的标准逻辑表达式,以便很方便地应用所选用的MSI组合功能件实现实际问题所要求的逻辑功能。

上一篇:MSI组合功能件的应用

公网安备44030402000607

公网安备44030402000607