数字逻辑电流的流动

发布时间:2014/4/16 20:39:31 访问次数:726

正如上一节讨论的,对于高频电流,最低阻CD4073BM96 抗(电感)信号回路是在与信号迹线直接相邻的平面内。在图10-30中给出四层印制电路板的分层显示中,对于最高层的信号,返回电流通路将是电源层。正如前面所讨论的,微带迹线中信号所产生的电力线终止于相邻平面,如图10-7所示,无论这个平面的作用是什么。在高频情况下,由于趋肤效应,场不会渗入平面,信号不知道在电源层下有接地层,因此返回电流将终止在电源层上。这会产生问题吗?返回电流在接地层上岂不是更好吗?为了回答这些问题,我们必须首先分析数字逻辑信号电流实际是如何流动的。

图10-30 -个普通的四层印制电路板的分层显示

许多工程师和设计师对于数字返回电流如何流动、在哪流动以及数字逻辑电流的源是什么都感到困惑。首先,让我声明驱动器IC不是电流的源;IC只是作为一个开关来控制电流。电流的源是去耦电容和(或)寄生迹线电容和负载电容。

从噪声或EMC的角度考虑,瞬态(开关)电流很重要,瞬态电流的流动不依赖于线路终端的负载(见图5-19的相关讨论)。因为沿线路的传播时间是有限的,瞬态电流不知道负载阻抗是什么样的,直到信号巳经穿过线路。

返回电流通路是传输线、带状线还是微带线结构的形式,依赖于逻辑转换是高对低还是低对高的转换。对于微带线,返回电流通路是什么形式也决定于迹线是临近接地层还是电源层。对于带状线,决定于迹线是位于两接地层之间、两电源层之间还是接地层和电源层之间。

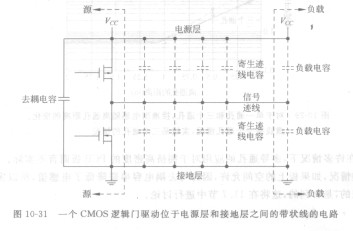

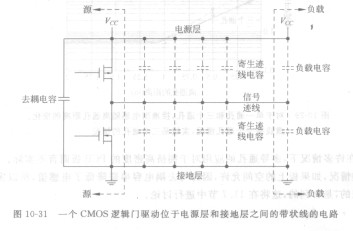

图10-31给出了一个具有带状线结构且输出信号迹线位于电源和接地层之间的CMOS逻辑门电路。在这个图里也标明了负载IC,源的去耦电容,信号迹线的寄生电容以及负载电容。图10-32~图10-37给出了各种可能结构的逻辑电流通路。

正如上一节讨论的,对于高频电流,最低阻CD4073BM96 抗(电感)信号回路是在与信号迹线直接相邻的平面内。在图10-30中给出四层印制电路板的分层显示中,对于最高层的信号,返回电流通路将是电源层。正如前面所讨论的,微带迹线中信号所产生的电力线终止于相邻平面,如图10-7所示,无论这个平面的作用是什么。在高频情况下,由于趋肤效应,场不会渗入平面,信号不知道在电源层下有接地层,因此返回电流将终止在电源层上。这会产生问题吗?返回电流在接地层上岂不是更好吗?为了回答这些问题,我们必须首先分析数字逻辑信号电流实际是如何流动的。

图10-30 -个普通的四层印制电路板的分层显示

许多工程师和设计师对于数字返回电流如何流动、在哪流动以及数字逻辑电流的源是什么都感到困惑。首先,让我声明驱动器IC不是电流的源;IC只是作为一个开关来控制电流。电流的源是去耦电容和(或)寄生迹线电容和负载电容。

从噪声或EMC的角度考虑,瞬态(开关)电流很重要,瞬态电流的流动不依赖于线路终端的负载(见图5-19的相关讨论)。因为沿线路的传播时间是有限的,瞬态电流不知道负载阻抗是什么样的,直到信号巳经穿过线路。

返回电流通路是传输线、带状线还是微带线结构的形式,依赖于逻辑转换是高对低还是低对高的转换。对于微带线,返回电流通路是什么形式也决定于迹线是临近接地层还是电源层。对于带状线,决定于迹线是位于两接地层之间、两电源层之间还是接地层和电源层之间。

图10-31给出了一个具有带状线结构且输出信号迹线位于电源和接地层之间的CMOS逻辑门电路。在这个图里也标明了负载IC,源的去耦电容,信号迹线的寄生电容以及负载电容。图10-32~图10-37给出了各种可能结构的逻辑电流通路。

公网安备44030402000607

公网安备44030402000607