数字集成电路的噪声容限

发布时间:2013/9/12 19:39:52 访问次数:4307

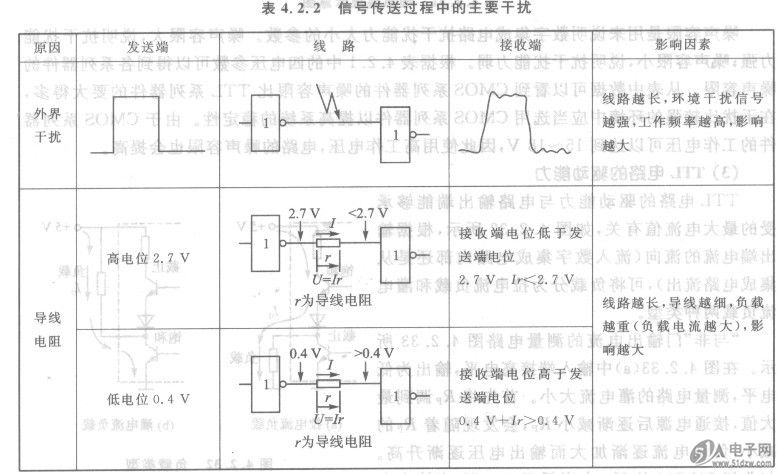

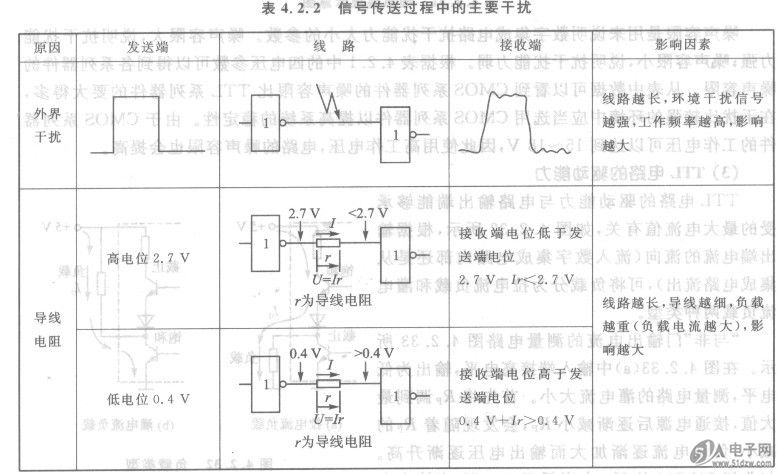

为保证数字集成电路信号的正确传输,SN74LV14APWR必须满足UOH≥U.H和UOL≤UIL。但在逻辑信号传送过程中,不可避免地会受到各种干扰,信号传送过程中的主要干扰如表4.2.2所列。

表4.2.2信号传送过程中的主要干扰

逻辑信号在传送过程中会受各种干扰而发生畸变,为保证信号的正碲传输,除了尽量减少各种干扰因素以外,器件本身的噪声容限指标(抗干扰能力)也是十分重要的。

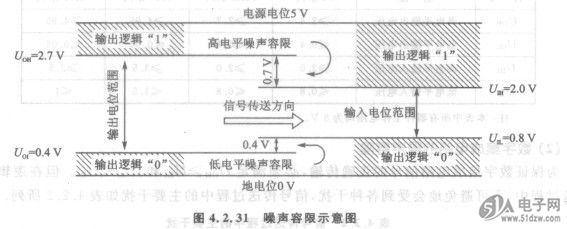

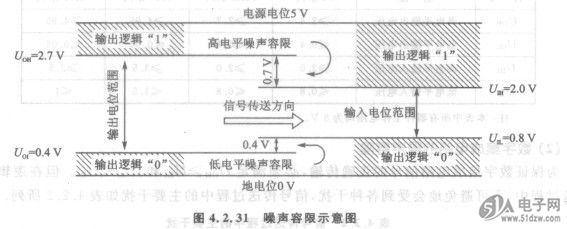

将表4.2.1中74LS系列的四电压参数表示在图4.2.31中,可以看到,当电路输出为逻辑“0”(低电平)时,输出电压最高为o.4 V。将此信号传送到另一个电路的输入端时,只要不超过0.8 V,输入端就能正确地接收。也就是说,允许信号在传送过程中受至咔干扰而产生的变化为0.4 V,这一变化范围称为低电平噪声容限,记为同理,从图中可以看出,高电平的噪声容限UH为0.7 V。

图4.2. 31噪声容限示意图

噪声容限是用来说明数字集成电路抗干扰能力大小的参数。噪声容限大,说明抗干扰能力强;噪声容限小,说明抗干扰能力弱。根据表4.2.1中的四电压参数可以得到各系列器件的噪声容限。从表中数据可以看到CMOS系列器件的噪声容限比TTL系列器件的要大得多,在干扰比较强的环境中应当选用CMOS系列器件以提高系统的稳定性。由于CMOS系列器件的工作电压可以达到15―18 V,因此使用高工作电压,电路的噪声容限也会提高。

为保证数字集成电路信号的正确传输,SN74LV14APWR必须满足UOH≥U.H和UOL≤UIL。但在逻辑信号传送过程中,不可避免地会受到各种干扰,信号传送过程中的主要干扰如表4.2.2所列。

表4.2.2信号传送过程中的主要干扰

逻辑信号在传送过程中会受各种干扰而发生畸变,为保证信号的正碲传输,除了尽量减少各种干扰因素以外,器件本身的噪声容限指标(抗干扰能力)也是十分重要的。

将表4.2.1中74LS系列的四电压参数表示在图4.2.31中,可以看到,当电路输出为逻辑“0”(低电平)时,输出电压最高为o.4 V。将此信号传送到另一个电路的输入端时,只要不超过0.8 V,输入端就能正确地接收。也就是说,允许信号在传送过程中受至咔干扰而产生的变化为0.4 V,这一变化范围称为低电平噪声容限,记为同理,从图中可以看出,高电平的噪声容限UH为0.7 V。

图4.2. 31噪声容限示意图

噪声容限是用来说明数字集成电路抗干扰能力大小的参数。噪声容限大,说明抗干扰能力强;噪声容限小,说明抗干扰能力弱。根据表4.2.1中的四电压参数可以得到各系列器件的噪声容限。从表中数据可以看到CMOS系列器件的噪声容限比TTL系列器件的要大得多,在干扰比较强的环境中应当选用CMOS系列器件以提高系统的稳定性。由于CMOS系列器件的工作电压可以达到15―18 V,因此使用高工作电压,电路的噪声容限也会提高。

上一篇:电压传输特性测试

上一篇:TTL电路的驱动能力

公网安备44030402000607

公网安备44030402000607