对FET的要求

发布时间:2012/5/22 19:10:47 访问次数:611

本电路是以电阻Rs作为源极负载的MSP430F147IPMR源极跟随器,所以要求无信号输入时的源极电流Is(叫做空载电流)要大于最大输出电流(其原因将在后面说明)。

按照设计指标最大输出电流为±ImA,所以设定源极电流Is =2 mA(最大输出电流的2倍)。

当输入大振幅信号,栅极电位下降到GND电位时,栅极一漏极间的电压等于电源电压VDD =15V。

因此,该电路中应选择IDSS在2mA以上,栅极一漏极间电压的最大额定电压VGDS在15V以上的JFET。显然,2SK184GR满足这些条件(参看表3.1)。

如果使用MOSFET,那么就不是IDSS,而是选择漏极电流的最大额定值小于流过电路的源极电流(一漏极电流),GDS大于电源电压的器件。

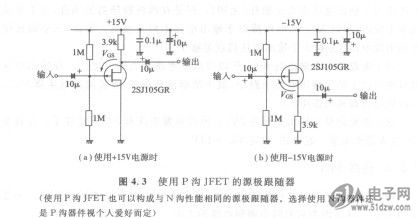

这里选择N沟JFET。使用P沟JFET的电路示于图4.3。与源极接地时相同,电路中将GND与电源调换。

本电路是以电阻Rs作为源极负载的MSP430F147IPMR源极跟随器,所以要求无信号输入时的源极电流Is(叫做空载电流)要大于最大输出电流(其原因将在后面说明)。

按照设计指标最大输出电流为±ImA,所以设定源极电流Is =2 mA(最大输出电流的2倍)。

当输入大振幅信号,栅极电位下降到GND电位时,栅极一漏极间的电压等于电源电压VDD =15V。

因此,该电路中应选择IDSS在2mA以上,栅极一漏极间电压的最大额定电压VGDS在15V以上的JFET。显然,2SK184GR满足这些条件(参看表3.1)。

如果使用MOSFET,那么就不是IDSS,而是选择漏极电流的最大额定值小于流过电路的源极电流(一漏极电流),GDS大于电源电压的器件。

这里选择N沟JFET。使用P沟JFET的电路示于图4.3。与源极接地时相同,电路中将GND与电源调换。

上一篇:输出与输入的波形是相同的

上一篇:偏置电路的设计

热门点击

热门点击

- 推挽型射极跟随器

- 使用PNP晶体管的射极跟随器

- 产品的质量保证等级

- 使用恒流负载的射极跟随器

- 引线键合失效

- 声表面波器件的特点和可靠性要求

- 频率特性与群延迟特性

- 外壳结构设计

- BiMOS集成电路

- 消除寄生效应的版图设计技术

推荐技术资料

推荐技术资料

- 泰克新发布的DSA830

- 泰克新发布的DSA8300在一台仪器中同时实现时域和频域分析,DS... [详细]

公网安备44030402000607

公网安备44030402000607