高可靠性EEPROM单元设计

发布时间:2012/4/23 19:56:52 访问次数:1933

这里介绍双层多晶硅FLOTOX EEPROM的单元NC7SZ32P5X可靠性设计问题。要使EE-PROM代表“1”和“O”状态,其擦除阈值电压和写入阈值电压之差必颏大于一定值。单元设计的目标是增大VTe、减少VTw。

要得到良好的EEPROM擦写特性,设计时采用的方法有:

①提高擦除耦合系数。

②减少隧道氧化层的厚度。

③增加擦除/写入时间。

④提高擦除/写入电压。

⑤减少隧道氧化层的面积。

增大两层多晶硅之间氧化层的面积Spp,减少其厚度Xpp就可以增大两层多晶硅之间的电容Cpp,从而提高了擦除耦合系数,但Spp增大,单元面积随之增大,使集成密度降低。减少两层多晶硅之间的厚度Xpp,虽然增大了Cpp,但由于两层多晶硅之间的氧化层质量难以控制,太薄会影响保持特性。所以Spp的选取应在擦除/写入效率和单元面积之间折中;Xpp的选取应在擦除/写入效率和保持特性之间折中。

减少隧道氧化层的厚度是提高EEPROM存储管擦写效率的有效措施。隧道氧化层越薄,其擦写效果越好。但隧道氧化层厚度的减少受到直接隧道效应电荷泄漏的限制,而且太薄的隧道氧化层工艺实现困难,隧道氧化层厚度的极限为6nm。为了进一步提高编程效率,同时又不使隧道氧化层太薄,可采用低势垒高度的隧道氧化层。

增加擦除/写入时间,可以提高擦写阈值之差,但延长擦/写时间会产生更多的陷阱电荷,从而影响EEPROM的可靠性。

提高擦写电压可以提高擦写阈值之差,但也有两个问题,一是擦写电压太高会使隧道氧化层击穿,造成EEPROM失效;二是工艺上实现20V以上的擦写电压比较困难(因为目前EEPROM的擦除/写入电压大多数都是在芯片内产生的)。

减少隧道氧化层的面积可以提高擦除/写入效率,同时也提高了单元的保持特性,所以设计时应尽量减少隧道氧化层的面积,一般由设计规则确定。

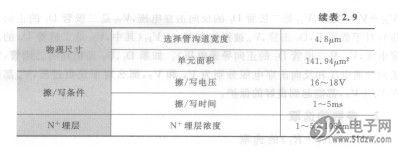

在EEPROM的设计时还要考虑两个重要的问题,一是使漏耦合系数尽可能减少,二是合理选取N+埋层的浓度。漏耦合电容不仅使EEPROM管的穿通电压减小,而且使输出特性曲线向上倾斜。所以在设讦时应尽可能使它减小。N+埋层浓度太低会影响写入效率,太高会影响隧道氧化层的质量,综合考虑后,N+埋层的掺杂浓度为1~5×l08/cm2。

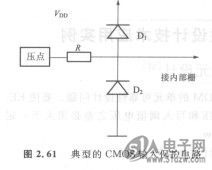

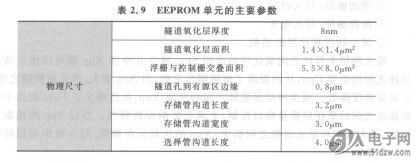

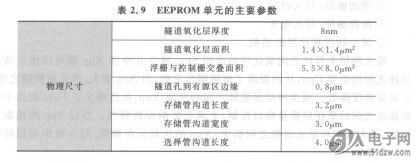

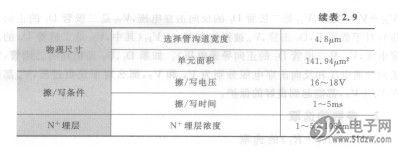

基于以上考虑,采用1. 41um设计规则设计的一种EEPROM单元如图2.61所示。表2.9给出了单元的主要参数。

这里介绍双层多晶硅FLOTOX EEPROM的单元NC7SZ32P5X可靠性设计问题。要使EE-PROM代表“1”和“O”状态,其擦除阈值电压和写入阈值电压之差必颏大于一定值。单元设计的目标是增大VTe、减少VTw。

要得到良好的EEPROM擦写特性,设计时采用的方法有:

①提高擦除耦合系数。

②减少隧道氧化层的厚度。

③增加擦除/写入时间。

④提高擦除/写入电压。

⑤减少隧道氧化层的面积。

增大两层多晶硅之间氧化层的面积Spp,减少其厚度Xpp就可以增大两层多晶硅之间的电容Cpp,从而提高了擦除耦合系数,但Spp增大,单元面积随之增大,使集成密度降低。减少两层多晶硅之间的厚度Xpp,虽然增大了Cpp,但由于两层多晶硅之间的氧化层质量难以控制,太薄会影响保持特性。所以Spp的选取应在擦除/写入效率和单元面积之间折中;Xpp的选取应在擦除/写入效率和保持特性之间折中。

减少隧道氧化层的厚度是提高EEPROM存储管擦写效率的有效措施。隧道氧化层越薄,其擦写效果越好。但隧道氧化层厚度的减少受到直接隧道效应电荷泄漏的限制,而且太薄的隧道氧化层工艺实现困难,隧道氧化层厚度的极限为6nm。为了进一步提高编程效率,同时又不使隧道氧化层太薄,可采用低势垒高度的隧道氧化层。

增加擦除/写入时间,可以提高擦写阈值之差,但延长擦/写时间会产生更多的陷阱电荷,从而影响EEPROM的可靠性。

提高擦写电压可以提高擦写阈值之差,但也有两个问题,一是擦写电压太高会使隧道氧化层击穿,造成EEPROM失效;二是工艺上实现20V以上的擦写电压比较困难(因为目前EEPROM的擦除/写入电压大多数都是在芯片内产生的)。

减少隧道氧化层的面积可以提高擦除/写入效率,同时也提高了单元的保持特性,所以设计时应尽量减少隧道氧化层的面积,一般由设计规则确定。

在EEPROM的设计时还要考虑两个重要的问题,一是使漏耦合系数尽可能减少,二是合理选取N+埋层的浓度。漏耦合电容不仅使EEPROM管的穿通电压减小,而且使输出特性曲线向上倾斜。所以在设讦时应尽可能使它减小。N+埋层浓度太低会影响写入效率,太高会影响隧道氧化层的质量,综合考虑后,N+埋层的掺杂浓度为1~5×l08/cm2。

基于以上考虑,采用1. 41um设计规则设计的一种EEPROM单元如图2.61所示。表2.9给出了单元的主要参数。

上一篇:一种正负输入的保护电路设计

热门点击

热门点击

公网安备44030402000607

公网安备44030402000607