电源钳位

发布时间:2012/4/22 16:46:48 访问次数:1111

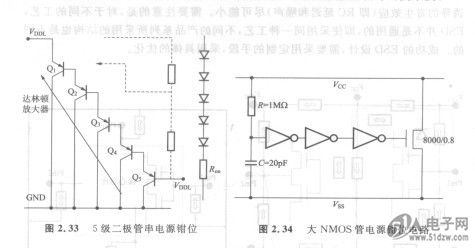

通常采用电源线钳位结构来保护19N10L集成电路免受ESD应力的冲击。对于电源钳位来讲,多指型gcNMOS和SCR是较好的结构。电源钳位通常放置在芯片的四个脚,连接到V DD和GND之间。如果存在多电源总线,放置在多个电源和多个地之间。另外一种电源钳位是基于正向二极管串,即5级二极管串电源钳位,使用snubbing电压驱动网络以减少达林顿效应(如图2.33所示)。由于二极管是用PNP来实现的,在工作中会出现达林顿复合效应,从而在ESD保护结构中出现不可忽视的泄漏。在高电流的条件下,PNP管的卢非常小,在SPICE模拟中可以使用二极管模式。为了避免由于达林顿效应而引起的内在泄漏,直接采用一个缓冲电阻来给最后一个晶体管Qs的发射极提供电流,以打断达林顿复合效应。

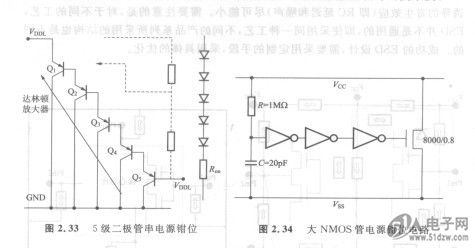

另外一个新颖的大尺寸NMOS电源钳位电路如图2.34所示。当存在电流瞬态时,电容将倒相器的输出接地,产生一个高的输出,以打开大尺寸NMOS,从而形成低阻抗的泄放通道以泄放ESD瞬态。这种电路的优点是利用通常的电路SPICE,ESD保护模块可以得到模拟。然而,这种电源钳位需要仔细的时序设计,而且占用较大的芯片面积,产生较大的寄生效应,也增大了版图设计的复杂度。

通常采用电源线钳位结构来保护19N10L集成电路免受ESD应力的冲击。对于电源钳位来讲,多指型gcNMOS和SCR是较好的结构。电源钳位通常放置在芯片的四个脚,连接到V DD和GND之间。如果存在多电源总线,放置在多个电源和多个地之间。另外一种电源钳位是基于正向二极管串,即5级二极管串电源钳位,使用snubbing电压驱动网络以减少达林顿效应(如图2.33所示)。由于二极管是用PNP来实现的,在工作中会出现达林顿复合效应,从而在ESD保护结构中出现不可忽视的泄漏。在高电流的条件下,PNP管的卢非常小,在SPICE模拟中可以使用二极管模式。为了避免由于达林顿效应而引起的内在泄漏,直接采用一个缓冲电阻来给最后一个晶体管Qs的发射极提供电流,以打断达林顿复合效应。

另外一个新颖的大尺寸NMOS电源钳位电路如图2.34所示。当存在电流瞬态时,电容将倒相器的输出接地,产生一个高的输出,以打开大尺寸NMOS,从而形成低阻抗的泄放通道以泄放ESD瞬态。这种电路的优点是利用通常的电路SPICE,ESD保护模块可以得到模拟。然而,这种电源钳位需要仔细的时序设计,而且占用较大的芯片面积,产生较大的寄生效应,也增大了版图设计的复杂度。

上一篇:输出ESD保护

上一篇:全芯片ESD保护电路

热门点击

热门点击

公网安备44030402000607

公网安备44030402000607