静态功耗

发布时间:2012/2/17 21:58:37 访问次数:5224

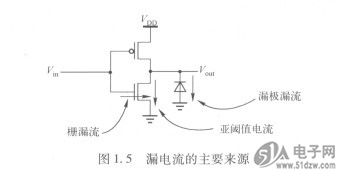

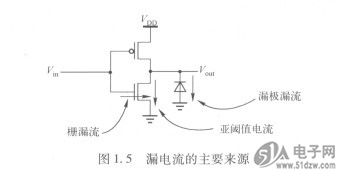

在理想情况下,PMOS和NMOS器件在稳态工作状况下不会同时导通,因此,1IK为0。但在CMOS电路中,总是存茌有漏电流。静态功耗主要是由漏电流引起的,漏电流的主要来源如图1.5所示,包括以下几种。SG7812AT-883B

(1)亚阈值漏流(Sub-threshold Leakage,/SUB):当晶体管处于弱反型时,从漏极到源极的电流。

(2)栅漏流(Gate Leakage,/CATE):由于栅氧隧道效应和热载流子注入,直接从栅电极经过栅氧化物到达衬底的电流。

(3)栅致漏极漏流(Gate Induced Drain Leakage,/GIDL):由于高的K,。在MOSFET的漏极形成高的场效应,而导致的从晶体管漏极到衬底的电流。

(4)反偏结漏流(Reverse Bias Junction Leakage,/REV):耗尽层中由于少子的漂移以及电子/空穴对的产生而引起的电流。

当电路工艺进入深亚微米和纳米阶段后,漏电流带来的静态功耗也成为集成电路的功耗组成的主要部分。

减少电源电压是降低动态功耗的最有效的方法。随着半导体工艺的按比例缩小( Scale),电源电压VDD己经从(低功耗器件)逐步降低。VDD的降低将导致低的晶体管开电流或者驱动电流/DS,从而阵低电路的速度。如果忽略90nm以下器件中的速度饱和效应以及其他二阶效应。

在90nm以上的工艺中,漏流引起的静态功耗要远远小于动态功耗,所以在这些工艺中采用此方法比较理想。但是随着工艺节点( node)进入90nm及65nm,静态功耗会增大到与动态功耗相当的地步,需要平衡动态功耗、静态功耗及性能之间的矛盾。

在理想情况下,PMOS和NMOS器件在稳态工作状况下不会同时导通,因此,1IK为0。但在CMOS电路中,总是存茌有漏电流。静态功耗主要是由漏电流引起的,漏电流的主要来源如图1.5所示,包括以下几种。SG7812AT-883B

(1)亚阈值漏流(Sub-threshold Leakage,/SUB):当晶体管处于弱反型时,从漏极到源极的电流。

(2)栅漏流(Gate Leakage,/CATE):由于栅氧隧道效应和热载流子注入,直接从栅电极经过栅氧化物到达衬底的电流。

(3)栅致漏极漏流(Gate Induced Drain Leakage,/GIDL):由于高的K,。在MOSFET的漏极形成高的场效应,而导致的从晶体管漏极到衬底的电流。

(4)反偏结漏流(Reverse Bias Junction Leakage,/REV):耗尽层中由于少子的漂移以及电子/空穴对的产生而引起的电流。

当电路工艺进入深亚微米和纳米阶段后,漏电流带来的静态功耗也成为集成电路的功耗组成的主要部分。

减少电源电压是降低动态功耗的最有效的方法。随着半导体工艺的按比例缩小( Scale),电源电压VDD己经从(低功耗器件)逐步降低。VDD的降低将导致低的晶体管开电流或者驱动电流/DS,从而阵低电路的速度。如果忽略90nm以下器件中的速度饱和效应以及其他二阶效应。

在90nm以上的工艺中,漏流引起的静态功耗要远远小于动态功耗,所以在这些工艺中采用此方法比较理想。但是随着工艺节点( node)进入90nm及65nm,静态功耗会增大到与动态功耗相当的地步,需要平衡动态功耗、静态功耗及性能之间的矛盾。

上一篇:冒险功耗

上一篇:选择低功耗的微处理器

热门点击

热门点击

公网安备44030402000607

公网安备44030402000607