ModeISim仿真软件设计流程

发布时间:2011/10/9 10:43:12 访问次数:2429

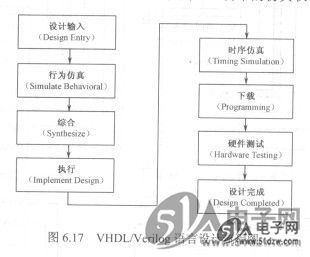

在使用ModeISim仿真软件之前,首先简单地介绍一下FPGA设计过程的基本流程,如图6.17所示。一个大型的项目,这些步骤是不能省略的。这其中行为仿真、时序仿真都需要用到ModelSim。对于一些简单的项目,也可以用ISE自带的仿真软件。 AT24C04

(1)设计输入(Design Entry)

设计输入是设计的第一步,其方式有许多种,如VHDLNerilog语言编程,原理图绘制(Schematic),状态机或真值表(Truthtable)及波形(Waveform)的输入等。将设计要求达到的目标采用上述的方式之一进行描述,是设计的第一步。

(2)行为仿真(Simulate Behavioral)

设计输入利用VHDLNerilog语言完成后,接下来要做的是行为仿真,也有文献将其称做功能仿真( Function Simulation)。行为所要达到的目标是功能上的验证。在做行为仿真时软件系统会自动对VHDLNerilog程序进衍语法上的检查、编译,以及将VHDL/Verilog行级的描述转化为结构化的门级电路,即综合( Synthesis)。通过了以上的综合之后便进入行为仿真步骤。行为仿真也可以在综合之前进行,但是不少设计者习惯先做综合之后再进行行为仿真,因为在综合中附带了语法上的检查、编译等功能,而且修改VHDLNerilog程序语法上的错误也比较方便。

进行行为仿真时使用的方法大多是将特定信号输入设计,然后观察设计输出的信号是否符合要求。做行为仿真时可能需要多次反复,对VHDL/Verilog源代码进行修改,等到所有的功能都正确后,才能进行下一个步骤。

(3)执行(Implement Design)

行为仿真之后就是执行,完成目标系统在器件上的布局与布线(Place&Route)。开发工具可产生含有时序延迟( Timing Delay)的VHDLNerilog网络表(Netlist)文件,这是最准确的时序延迟文件。

(4)时序仿真(Timing Simulation)

执行完成后,建议在硬件测试之前先做时序仿真,将其作为最后一道把关工作。当然,不做时序仿真,直接将执行结果送到电路板上进行测试也可以。因为做仿真需要输入正确、完整的测试模型( pattern)。如果测试模型不正确或是其代表性不够,就算做了仿真也不能确保结果正确。但是,在硬件测试之前,通过软件进行检查,确保无误后再做硬件效率更高一些。

(5)下载

程序将被转换成位流文件写入芯片中以实现芯片功能,软件部分由器件厂商提供的专用软件完成,硬件则需要使用专用的下载线,通过微机的通信接口与系统板连接。

(6)硬件测试

对实物(芯片及其外围电路构成的系统)进行实际测试,完成设计。

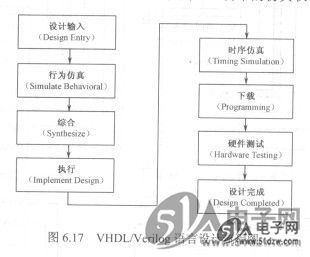

在使用ModeISim仿真软件之前,首先简单地介绍一下FPGA设计过程的基本流程,如图6.17所示。一个大型的项目,这些步骤是不能省略的。这其中行为仿真、时序仿真都需要用到ModelSim。对于一些简单的项目,也可以用ISE自带的仿真软件。 AT24C04

(1)设计输入(Design Entry)

设计输入是设计的第一步,其方式有许多种,如VHDLNerilog语言编程,原理图绘制(Schematic),状态机或真值表(Truthtable)及波形(Waveform)的输入等。将设计要求达到的目标采用上述的方式之一进行描述,是设计的第一步。

(2)行为仿真(Simulate Behavioral)

设计输入利用VHDLNerilog语言完成后,接下来要做的是行为仿真,也有文献将其称做功能仿真( Function Simulation)。行为所要达到的目标是功能上的验证。在做行为仿真时软件系统会自动对VHDLNerilog程序进衍语法上的检查、编译,以及将VHDL/Verilog行级的描述转化为结构化的门级电路,即综合( Synthesis)。通过了以上的综合之后便进入行为仿真步骤。行为仿真也可以在综合之前进行,但是不少设计者习惯先做综合之后再进行行为仿真,因为在综合中附带了语法上的检查、编译等功能,而且修改VHDLNerilog程序语法上的错误也比较方便。

进行行为仿真时使用的方法大多是将特定信号输入设计,然后观察设计输出的信号是否符合要求。做行为仿真时可能需要多次反复,对VHDL/Verilog源代码进行修改,等到所有的功能都正确后,才能进行下一个步骤。

(3)执行(Implement Design)

行为仿真之后就是执行,完成目标系统在器件上的布局与布线(Place&Route)。开发工具可产生含有时序延迟( Timing Delay)的VHDLNerilog网络表(Netlist)文件,这是最准确的时序延迟文件。

(4)时序仿真(Timing Simulation)

执行完成后,建议在硬件测试之前先做时序仿真,将其作为最后一道把关工作。当然,不做时序仿真,直接将执行结果送到电路板上进行测试也可以。因为做仿真需要输入正确、完整的测试模型( pattern)。如果测试模型不正确或是其代表性不够,就算做了仿真也不能确保结果正确。但是,在硬件测试之前,通过软件进行检查,确保无误后再做硬件效率更高一些。

(5)下载

程序将被转换成位流文件写入芯片中以实现芯片功能,软件部分由器件厂商提供的专用软件完成,硬件则需要使用专用的下载线,通过微机的通信接口与系统板连接。

(6)硬件测试

对实物(芯片及其外围电路构成的系统)进行实际测试,完成设计。

热门点击

热门点击

- 三极管结构及工作原理

- 判断耳机好坏的方法与判断喇叭好坏的方法基本相

- 贴片元件手工焊接工艺

- 声控开关电路

- 电灯多地控制线路

- 电容器的电容误差

- 可变电阻器结构和工作原理

- 音频功率放大电路

- 印制电路板设计的一般步骤

- 绝缘栅场效应管

推荐技术资料

推荐技术资料

- 自制经典的1875功放

- 平时我也经常逛一些音响DIY论坛,发现有很多人喜欢LM... [详细]

公网安备44030402000607

公网安备44030402000607