使用专用加密解密单元的AES-Hash也有扩展精度的浮点计算

发布时间:2023/12/16 15:26:15 访问次数:64

传统X86程序几乎都会覆盖到4个端口的执行单元,分支跳转,地址加载,偏移地址和逻辑计算等指令在程序中都有不小占比,可以预见,执行越传统的X86程序,有机会带来越高的超线程提升,而使用向量程序则不会,为此我做了一个简单的验证。

AIDA64的性能测试非常有意思,我将其进行一个归类这些程序包含了传统指令的分支预测,图片处理,视频压缩编码(SSE4.1),也有高内存带宽,高向量化的程序,也有使用专用加密解密单元的AES-Hash,也有扩展精度的浮点计算。

AMD在支持SHA指令集的情况下,还具备双倍于Intel的AES单元(4个),这样在AES和SHA的超线程提升上也明显高于Intel,值得注意的是,8121U也有SHA指令集,也拥有加强的AES单元,所以他的AES/Hash性能也非常出色,超线程性能也超越了Intel其他处理器

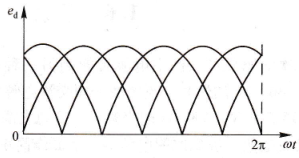

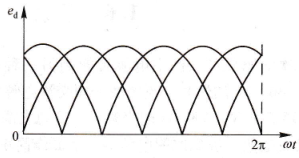

电路中的BJT改用PNP型管时,有哪些元器件的连接需要改变?作如此变动后,若在输人信号os(正弦波)的正半周,输出信号″。

由上一节的分析可知,静态工作点Q是很重要的,它不但决定了放大电路静态工作点的稳定问题.

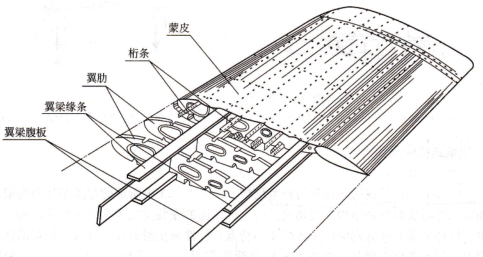

电路是分立元件电路中最常用的稳定静态T作点的共射极放大电路。

它的基极一射极偏置电路由ycc、基极电阻Rbl、rb2和射极电阻Re组成,常称为基极分压式射极偏置电路c它的直流通路。

这四个端口都有X86传统指令执行单元,包括传统的ALU,分支跳转,地址偏移和加载,移位等指令,而向量端口只有三个,即0,1,5,其中非AVX512的处理器,也就是除了X299以外的酷睿处理器,除了向量逻辑,向量shuffle(寄存器数据重排)会使用端口5,主要将使用0和1两个端口。

传统X86程序几乎都会覆盖到4个端口的执行单元,分支跳转,地址加载,偏移地址和逻辑计算等指令在程序中都有不小占比,可以预见,执行越传统的X86程序,有机会带来越高的超线程提升,而使用向量程序则不会,为此我做了一个简单的验证。

AIDA64的性能测试非常有意思,我将其进行一个归类这些程序包含了传统指令的分支预测,图片处理,视频压缩编码(SSE4.1),也有高内存带宽,高向量化的程序,也有使用专用加密解密单元的AES-Hash,也有扩展精度的浮点计算。

AMD在支持SHA指令集的情况下,还具备双倍于Intel的AES单元(4个),这样在AES和SHA的超线程提升上也明显高于Intel,值得注意的是,8121U也有SHA指令集,也拥有加强的AES单元,所以他的AES/Hash性能也非常出色,超线程性能也超越了Intel其他处理器

电路中的BJT改用PNP型管时,有哪些元器件的连接需要改变?作如此变动后,若在输人信号os(正弦波)的正半周,输出信号″。

由上一节的分析可知,静态工作点Q是很重要的,它不但决定了放大电路静态工作点的稳定问题.

电路是分立元件电路中最常用的稳定静态T作点的共射极放大电路。

它的基极一射极偏置电路由ycc、基极电阻Rbl、rb2和射极电阻Re组成,常称为基极分压式射极偏置电路c它的直流通路。

这四个端口都有X86传统指令执行单元,包括传统的ALU,分支跳转,地址偏移和加载,移位等指令,而向量端口只有三个,即0,1,5,其中非AVX512的处理器,也就是除了X299以外的酷睿处理器,除了向量逻辑,向量shuffle(寄存器数据重排)会使用端口5,主要将使用0和1两个端口。

公网安备44030402000607

公网安备44030402000607