交互式的布线引擎来自动解决单CPU操作的更高性能

发布时间:2021/12/11 17:15:48 访问次数:1440

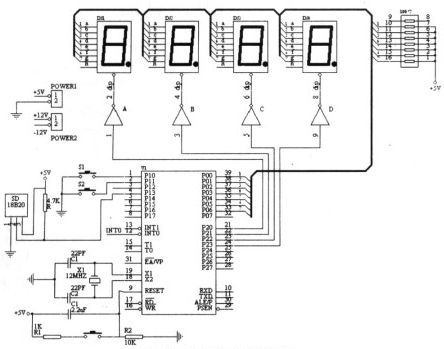

Altium提供增强的过孔功能,并允许在不同信号层上使用不同尺寸的焊盘。过孔的叠加可以支持更高的跟踪密度。工程师还可以通过元件焊盘来实现过孔的偏移。

所有上述的增强型功能都提高了PCB设计的精确性,并为设计板布线和可视化提供了新的设计思路。

优化三维PCB图形引擎至关重要,由此可以极大的提高整个软件的性能,并降低对硬件的要求,使得系统的反应速度更快,把图形延迟对设计造成的影响变得最小。

Altium同时还通过交互式的布线引擎来自动解决布线中遇到障碍需要改变各种路径的各种情况。

平衡的TSETUP/THOLD位于接收器端的RCLK和RDATA之间

接收器上的可调整PTO(逐步开启)LVCMOS输出将EMI和SSO效应减小到最低限度

@Speed BIST使LVDS传输路径生效

所有LVCMOS输入和控制引脚都具有内部下拉

用于PLL的片上滤波器位于发送器和接收器上

发送器具有48引脚TQFP封装,接收器采用64引脚TQPF封装

该系统还带来了一个新的超高效的核存储架构,可提供单CPU操作的更高性能、更高容量的设计收敛。使用这个新系统,设计师们实现了设计时间、设计闭合的显著提高,以及先进数字和混合信号产品更快的上市时间。

另外,它还引入了多项新的、改进的实现与设计收敛技术,包括自动化布局综合、端到端multi-mode multi-corner优化、variation-tolerant和低功耗时钟树及时钟网综合、高容量布局和优化、32纳米布线和基于制造考量的优化、signoff-driven的实现以及flip chip设计等特性。

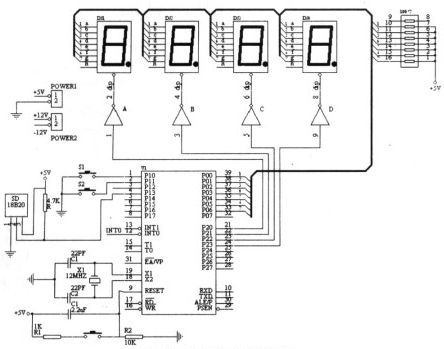

Altium提供增强的过孔功能,并允许在不同信号层上使用不同尺寸的焊盘。过孔的叠加可以支持更高的跟踪密度。工程师还可以通过元件焊盘来实现过孔的偏移。

所有上述的增强型功能都提高了PCB设计的精确性,并为设计板布线和可视化提供了新的设计思路。

优化三维PCB图形引擎至关重要,由此可以极大的提高整个软件的性能,并降低对硬件的要求,使得系统的反应速度更快,把图形延迟对设计造成的影响变得最小。

Altium同时还通过交互式的布线引擎来自动解决布线中遇到障碍需要改变各种路径的各种情况。

平衡的TSETUP/THOLD位于接收器端的RCLK和RDATA之间

接收器上的可调整PTO(逐步开启)LVCMOS输出将EMI和SSO效应减小到最低限度

@Speed BIST使LVDS传输路径生效

所有LVCMOS输入和控制引脚都具有内部下拉

用于PLL的片上滤波器位于发送器和接收器上

发送器具有48引脚TQFP封装,接收器采用64引脚TQPF封装

该系统还带来了一个新的超高效的核存储架构,可提供单CPU操作的更高性能、更高容量的设计收敛。使用这个新系统,设计师们实现了设计时间、设计闭合的显著提高,以及先进数字和混合信号产品更快的上市时间。

另外,它还引入了多项新的、改进的实现与设计收敛技术,包括自动化布局综合、端到端multi-mode multi-corner优化、variation-tolerant和低功耗时钟树及时钟网综合、高容量布局和优化、32纳米布线和基于制造考量的优化、signoff-driven的实现以及flip chip设计等特性。

公网安备44030402000607

公网安备44030402000607