SRAM结构PIM技术双核架构的优点

发布时间:2020/11/11 0:04:43 访问次数:1628

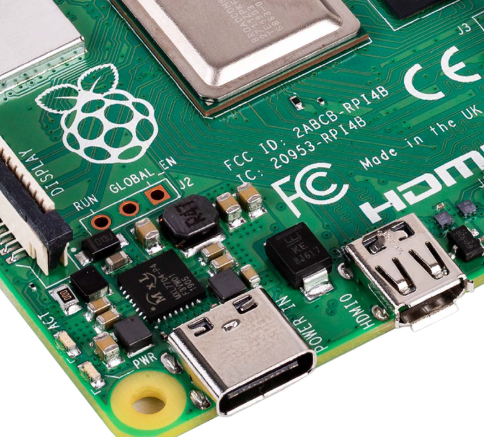

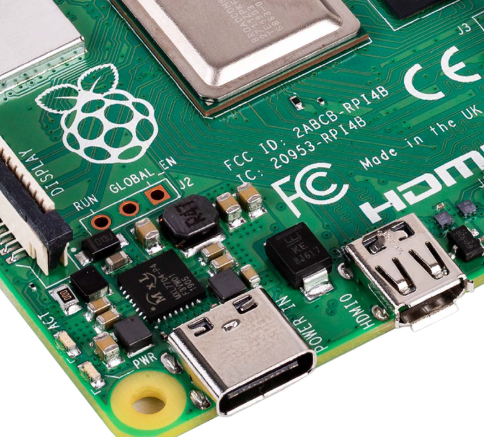

工业控制的人机交互界面,因为双核的存在,所以客户可以自由地分配任务给两个内核进行不同的任务,如将人机界面显示的控制放在Cortex-M7进行处理,实时控制部分,如说网关通讯、马达驱动以及传感器数据采集放在实时的处理内核Cortex-M4上面。在家庭自动化以及安全模块上, Cortex-M7可以处理人工智能的神经网络,包括它所应用到的如图象显示、语音的识别、图象的识别等;Cortex-M4的内核处理实时性的,如Wi-Fi的通讯、以太网等实时通讯的模块上。

对于,Renaud BOUZEREAU主要总结了四个方面:增加系统效能、增加系统效率、缩短开发周期、降低系统成本。

两个核可以独立运行,可以进行两套不同的任务,或者是执行一套任务,由另外一个核监控着另外一个核的应用的运行情况,来保证它的安全性。在这样的架构下,可以减少运算时间及应用中的平均功耗。

在电源架构上,STM32H7双核产品分为三个供电域,分别是高性能域,是由Cortex-M7在里头进行GUI、DSP和安全的控制,第二的Cortex-M4主要处理实时性的连接和控制,比如说对外的连接,实时操作系统,马达驱动以及更多的控制任务。第三个域称为大数据量采集域,另外两个域在休眠的时候,这个域自动的从传感器,包括外部的电压电流进行数据采集,采集完之后,达到一定数量或者达到一定阈值后可以唤醒另外两个域进行处理。在三个域里可以自由分配工作时序,自由去决定开启和关闭的过程,从而达到整体的动态功耗的平衡。

因为STM32H7的两个核是独立工作的,可以直接安排两个或者多个任务在双核进行处理。所以在开发过程中,里面的配置包括内部资源,只要在分配好之后,两个团队就可以基于自己的内核或者自己分配的资源进行开发,从而不用去避免会影响到另外一个团队的工作,从而可以缩短电路板设计和项目评估时间。

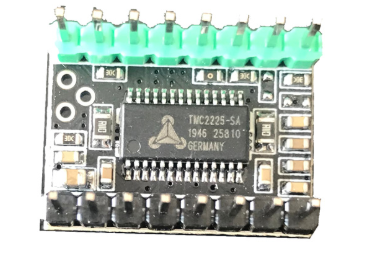

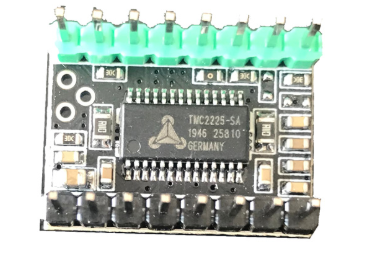

全新AI加速器,可高速且低功耗地执行CNN(卷积神经网络)处理,向下一代瑞萨嵌入式人工智能(e-AI)迈进,加速端点设备智能化。采用该加速器的测试芯片效率达到业界最高水平8.8 TOPS/W。瑞萨加速器基于计算存储一体化(PIM)架构,即当读取存储器数据时,在存储器电路中执行乘法和累加运算。

三进制(-1,0,1)SRAM结构PIM技术采用三元存储器与简单数字计算块相组合,保证硬件数量增加的同时将计算误差降至最低。同时,允许根据所需精度进行位数切换(如1.5位(三进制)和4位计算之间)。可针对不同用户需求支持不同的精度及运算规模,用户可优化精度与功耗间的平衡。

当采用PIM架构时,通过检测SRAM结构中的位线电流值以读取存储器数据。尽管使用A/D转换器进行高精度位线电流检测是有效的,但这种方法功耗高且芯片面积较大。

(素材来源:eccn.如涉版权请联系删除。特别感谢)

工业控制的人机交互界面,因为双核的存在,所以客户可以自由地分配任务给两个内核进行不同的任务,如将人机界面显示的控制放在Cortex-M7进行处理,实时控制部分,如说网关通讯、马达驱动以及传感器数据采集放在实时的处理内核Cortex-M4上面。在家庭自动化以及安全模块上, Cortex-M7可以处理人工智能的神经网络,包括它所应用到的如图象显示、语音的识别、图象的识别等;Cortex-M4的内核处理实时性的,如Wi-Fi的通讯、以太网等实时通讯的模块上。

对于,Renaud BOUZEREAU主要总结了四个方面:增加系统效能、增加系统效率、缩短开发周期、降低系统成本。

两个核可以独立运行,可以进行两套不同的任务,或者是执行一套任务,由另外一个核监控着另外一个核的应用的运行情况,来保证它的安全性。在这样的架构下,可以减少运算时间及应用中的平均功耗。

在电源架构上,STM32H7双核产品分为三个供电域,分别是高性能域,是由Cortex-M7在里头进行GUI、DSP和安全的控制,第二的Cortex-M4主要处理实时性的连接和控制,比如说对外的连接,实时操作系统,马达驱动以及更多的控制任务。第三个域称为大数据量采集域,另外两个域在休眠的时候,这个域自动的从传感器,包括外部的电压电流进行数据采集,采集完之后,达到一定数量或者达到一定阈值后可以唤醒另外两个域进行处理。在三个域里可以自由分配工作时序,自由去决定开启和关闭的过程,从而达到整体的动态功耗的平衡。

因为STM32H7的两个核是独立工作的,可以直接安排两个或者多个任务在双核进行处理。所以在开发过程中,里面的配置包括内部资源,只要在分配好之后,两个团队就可以基于自己的内核或者自己分配的资源进行开发,从而不用去避免会影响到另外一个团队的工作,从而可以缩短电路板设计和项目评估时间。

全新AI加速器,可高速且低功耗地执行CNN(卷积神经网络)处理,向下一代瑞萨嵌入式人工智能(e-AI)迈进,加速端点设备智能化。采用该加速器的测试芯片效率达到业界最高水平8.8 TOPS/W。瑞萨加速器基于计算存储一体化(PIM)架构,即当读取存储器数据时,在存储器电路中执行乘法和累加运算。

三进制(-1,0,1)SRAM结构PIM技术采用三元存储器与简单数字计算块相组合,保证硬件数量增加的同时将计算误差降至最低。同时,允许根据所需精度进行位数切换(如1.5位(三进制)和4位计算之间)。可针对不同用户需求支持不同的精度及运算规模,用户可优化精度与功耗间的平衡。

当采用PIM架构时,通过检测SRAM结构中的位线电流值以读取存储器数据。尽管使用A/D转换器进行高精度位线电流检测是有效的,但这种方法功耗高且芯片面积较大。

(素材来源:eccn.如涉版权请联系删除。特别感谢)

热门点击

热门点击

- DSP48E2片低精度MAC运算激活参数数据

- 硅光电倍增管传感器的响应时间和高检测效率

- 隔离变压器的负载防振荡

- 集成式环境光和接近光传感器

- 通信接口多通道低价格的模数转换器

- 开关稳压器同步振荡器频率

- 逻辑电平电压接近于电源电压

- SRAM结构PIM技术双核架构的优点

- BNC转SMA高性能屏蔽线双路低噪声

- 新型XGS传感器技术FPGA开发环境的接口

推荐技术资料

推荐技术资料

- 中国传媒大学传媒博物馆开

- 传媒博物馆开馆仪式隆童举行。教育都i国家广电总局等部门... [详细]

公网安备44030402000607

公网安备44030402000607