降压型开关稳压器电流闭环控制原理

发布时间:2020/10/16 21:50:06 访问次数:2099

提高集成度和抽象水平多少可以降低一些复杂性和不确定性,并有助于将整体复杂性保持在人类设计师能够理解和应付的范围内。正如任何会在设计后期增加其影响力的科目一样,上游设计假设与决策可能会形成额外的复杂性与不确定性来源,如果能够较早地协调与交流,可以最大程度地减小这些复杂性与不确定性。

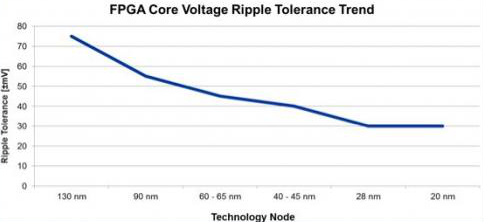

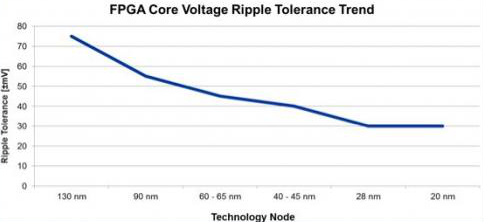

电源设计是在复杂性日益增加的系统中这些潜在的下游科目之一。在本例中,让我们从电源设计师的角度看一下复杂性和不确定性的来源。影响电源设计的两个关键FPGA因素是电压和电流要求。

FPGA电压要求趋势正在推升复杂性,因为它们要求日益增多的电源轨。

虽然占空比有最大限制,但本电源管理技巧重点探讨占空比的最小限制。

在连续导通模式(CCM)下,降压型开关稳压器(降压变换器)的占空比相当于输出电压除以输入电压。因此如果输出电压正好是输入电压的一半,对应的占空比为 50%。根据实际分量和相应的寄生损失,这个占空比实际上稍有不同。不过这个简单的占空比计算公式已足够用于估算。

采用ADP2389的典型降压型开关稳压器,最高输出电流为12 A

通过5 V电源电压产生1 V输出电压,对应的占空比为20%。采用ADI公司ADP2389稳压器的降压转换器拓扑。该稳压器的开关频率可高达2.2 MHz。在图2的时域图中,可以看到当开关频率为2.2 Mhz时,在新周期开始之前,周期T值只有大约450 ns。

此电流用于过流保护,并用于根据电流闭环控制原理(电流模式控制)工作的稳压器中。环路调节也需要测量电感电流。

在开关瞬变后,必须先降低产生的噪音才能进行准确的电流测量。这需要一些时间,也称为消隐时间。尤其对于MHz级别的极高开关频率,最小导通时间的影响也更大,目前正在研发能够实现更短的最小导通时间的电路。

对于低占空比,例如降压型开关稳压器中的高输入电压和低输出电压,最小导通时间是关键限制。它通常会限制支持开关模式电源工作的最大开关频率。

(素材来源:eccn.如涉版权请联系删除。特别感谢)

提高集成度和抽象水平多少可以降低一些复杂性和不确定性,并有助于将整体复杂性保持在人类设计师能够理解和应付的范围内。正如任何会在设计后期增加其影响力的科目一样,上游设计假设与决策可能会形成额外的复杂性与不确定性来源,如果能够较早地协调与交流,可以最大程度地减小这些复杂性与不确定性。

电源设计是在复杂性日益增加的系统中这些潜在的下游科目之一。在本例中,让我们从电源设计师的角度看一下复杂性和不确定性的来源。影响电源设计的两个关键FPGA因素是电压和电流要求。

FPGA电压要求趋势正在推升复杂性,因为它们要求日益增多的电源轨。

虽然占空比有最大限制,但本电源管理技巧重点探讨占空比的最小限制。

在连续导通模式(CCM)下,降压型开关稳压器(降压变换器)的占空比相当于输出电压除以输入电压。因此如果输出电压正好是输入电压的一半,对应的占空比为 50%。根据实际分量和相应的寄生损失,这个占空比实际上稍有不同。不过这个简单的占空比计算公式已足够用于估算。

采用ADP2389的典型降压型开关稳压器,最高输出电流为12 A

通过5 V电源电压产生1 V输出电压,对应的占空比为20%。采用ADI公司ADP2389稳压器的降压转换器拓扑。该稳压器的开关频率可高达2.2 MHz。在图2的时域图中,可以看到当开关频率为2.2 Mhz时,在新周期开始之前,周期T值只有大约450 ns。

此电流用于过流保护,并用于根据电流闭环控制原理(电流模式控制)工作的稳压器中。环路调节也需要测量电感电流。

在开关瞬变后,必须先降低产生的噪音才能进行准确的电流测量。这需要一些时间,也称为消隐时间。尤其对于MHz级别的极高开关频率,最小导通时间的影响也更大,目前正在研发能够实现更短的最小导通时间的电路。

对于低占空比,例如降压型开关稳压器中的高输入电压和低输出电压,最小导通时间是关键限制。它通常会限制支持开关模式电源工作的最大开关频率。

(素材来源:eccn.如涉版权请联系删除。特别感谢)

上一篇:内核电压纹波容差的公开幅度降低

上一篇:电网电压的交流电压提升至直流

热门点击

热门点击

- 晶体管的阈值电压屏障降低

- n型温差电元件金属导体电极

- 通用LED驱动器主要特点

- 数字电源和电机控制混合储能系统

- 调节频率发生器输出的频率

- 抗硫芯片电阻器数据显示电路

- 模拟和数字控制接口硬件调整

- 硅光电晶体管光学耦合隔离电压

- IC内置的数字控制系统和负载情况

- 探针夹或SMA-2-BNC连接器电流

推荐技术资料

推荐技术资料

- DS2202型示波器试用

- 说起数字示波器,普源算是国内的老牌子了,FQP8N60... [详细]

公网安备44030402000607

公网安备44030402000607