噪声和调制器时钟频率数字音频应用

发布时间:2020/9/19 23:28:33 访问次数:6064

EVB三阶滤波器的-3 dB截止频率为76 kHz,在500 kHz下仅衰减-31 db。这款低通滤波器具备出色的带内平坦性,但带外衰减必须大幅改善,即使是限于纯粹的重构音频应用。要抑制DAC成型噪声和调制器时钟频率MCLK,就必须满足这一点。

根据软件DDS的具体使用,用于单信号音生成器或任意波形生成器(生成复杂波形时为AWG),必须优化AAF,以解决带外衰减或群延迟失真。以大家熟悉的SRS DS360超低失真函数生成器为例进行比较,采用7阶Cauer AAF可达到类似的采样速率。

信号重构由AD1862完成,后者是一款串行输入20位分段R-2R DAC,适用于数字音频应用。AD1862在高达768 kHz (×16 fS)频率下可以保持20位字采样速率,且具备出色的噪声和线性度。它支持单端电流输出,所以能够使用最出色的放大器来实施外部I-V转换。

集成电路工艺进入先进节点(Advanced Node),以及应用场景的不断增加,带来芯片设计规模越来越大以及时钟结构更加复杂,针对时钟结构的分析与时钟的实现也更加困难。就时钟树综合(Clock Tree Synthesis,CTS)而言,时钟结构复杂程度的增加,可能会带来公共路径(Common Path)的长度减少,片上误差(On Chip Variation,OCV)的影响增加,CTS迭代时间(Turn-Around Time)增加,以及时钟上功耗增加等问题。因此,在物理实现中,CTS变得越来越重要。

借助于Cadence公司的自动化布局布线工具Innovus,探讨了针对复杂时钟结构的时钟如何进行分析,其次基于分析结果提出时钟实现上可能出现的问题以及解决方案,基于调整进行CTS实现,并与传统CTS方案的结果进行对比,进行总结并对结论进行进一步分析。

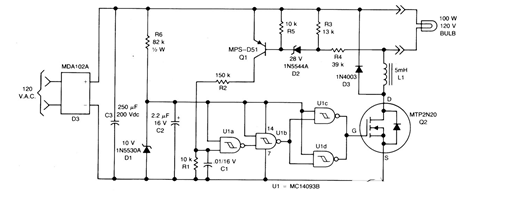

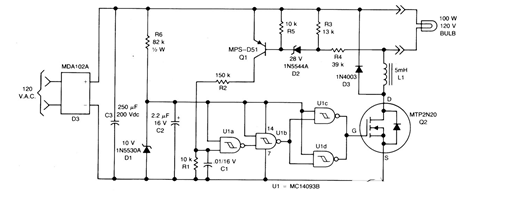

可变降压电路的输入使用AC /DC 电源提供的48V 总线,这部分电路根据后接的LED 颗数多少和输出电流大小, 动态调节输出, 使其输出电压和LED 灯串电压的差额保持较小的水平,从而减小大电流下三极管的损耗。

使用LM5010 降压芯片来搭建可变降压电路,LM5010 是一个恒定导通时间的Buck 控制芯片。R1 和R2 组成电压反馈电路,将输出电压进行分压后输入至FB 脚上。

每当FB 脚上电压低于2. 5V 时,芯片内部的开关会固定的导通一段时间,导通时间与输入电压和Ron有关, 之后开关会关断265ns 或直至FB 脚上电压下降到2. 5V 以下。电路通过(R1 + R2) /R2・VFB来设定最大输出电压。另一方面,为了降低在三极管的功率损耗,我们同时监测采集三极管和采样电阻的压降和, 并使用LM358 进行正向放大后通过D2 输入到FB 脚上。

在三极管和采样电阻上的压降总和就不会大于Vdrop = ( VFB + VD2) × R3 / ( R3 + R4)。因此当LED灯串上的电压小于LM5010 的最大输出电压时,多余的电压就会由三极管和采样电阻承担,当这个电压经过放大后大于FB 脚的阈值时,LM5010 延长开关关断时间,使输出电压下降,因此最终的Vout =Vled + Vdrop。从而在LED 颗数比设计值少或者在对LED 进行调光时,前端输出的电压能够更合理的匹配灯串电压。

(素材:chinaaet.如涉版权请联系删除)

EVB三阶滤波器的-3 dB截止频率为76 kHz,在500 kHz下仅衰减-31 db。这款低通滤波器具备出色的带内平坦性,但带外衰减必须大幅改善,即使是限于纯粹的重构音频应用。要抑制DAC成型噪声和调制器时钟频率MCLK,就必须满足这一点。

根据软件DDS的具体使用,用于单信号音生成器或任意波形生成器(生成复杂波形时为AWG),必须优化AAF,以解决带外衰减或群延迟失真。以大家熟悉的SRS DS360超低失真函数生成器为例进行比较,采用7阶Cauer AAF可达到类似的采样速率。

信号重构由AD1862完成,后者是一款串行输入20位分段R-2R DAC,适用于数字音频应用。AD1862在高达768 kHz (×16 fS)频率下可以保持20位字采样速率,且具备出色的噪声和线性度。它支持单端电流输出,所以能够使用最出色的放大器来实施外部I-V转换。

集成电路工艺进入先进节点(Advanced Node),以及应用场景的不断增加,带来芯片设计规模越来越大以及时钟结构更加复杂,针对时钟结构的分析与时钟的实现也更加困难。就时钟树综合(Clock Tree Synthesis,CTS)而言,时钟结构复杂程度的增加,可能会带来公共路径(Common Path)的长度减少,片上误差(On Chip Variation,OCV)的影响增加,CTS迭代时间(Turn-Around Time)增加,以及时钟上功耗增加等问题。因此,在物理实现中,CTS变得越来越重要。

借助于Cadence公司的自动化布局布线工具Innovus,探讨了针对复杂时钟结构的时钟如何进行分析,其次基于分析结果提出时钟实现上可能出现的问题以及解决方案,基于调整进行CTS实现,并与传统CTS方案的结果进行对比,进行总结并对结论进行进一步分析。

可变降压电路的输入使用AC /DC 电源提供的48V 总线,这部分电路根据后接的LED 颗数多少和输出电流大小, 动态调节输出, 使其输出电压和LED 灯串电压的差额保持较小的水平,从而减小大电流下三极管的损耗。

使用LM5010 降压芯片来搭建可变降压电路,LM5010 是一个恒定导通时间的Buck 控制芯片。R1 和R2 组成电压反馈电路,将输出电压进行分压后输入至FB 脚上。

每当FB 脚上电压低于2. 5V 时,芯片内部的开关会固定的导通一段时间,导通时间与输入电压和Ron有关, 之后开关会关断265ns 或直至FB 脚上电压下降到2. 5V 以下。电路通过(R1 + R2) /R2・VFB来设定最大输出电压。另一方面,为了降低在三极管的功率损耗,我们同时监测采集三极管和采样电阻的压降和, 并使用LM358 进行正向放大后通过D2 输入到FB 脚上。

在三极管和采样电阻上的压降总和就不会大于Vdrop = ( VFB + VD2) × R3 / ( R3 + R4)。因此当LED灯串上的电压小于LM5010 的最大输出电压时,多余的电压就会由三极管和采样电阻承担,当这个电压经过放大后大于FB 脚的阈值时,LM5010 延长开关关断时间,使输出电压下降,因此最终的Vout =Vled + Vdrop。从而在LED 颗数比设计值少或者在对LED 进行调光时,前端输出的电压能够更合理的匹配灯串电压。

(素材:chinaaet.如涉版权请联系删除)

上一篇:三块控制器的控制芯片管脚功能

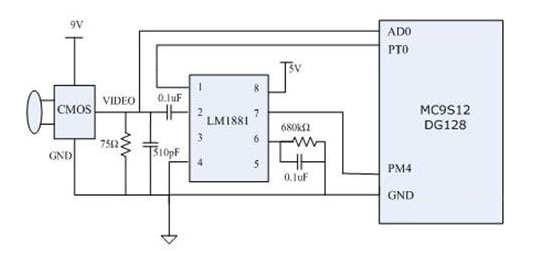

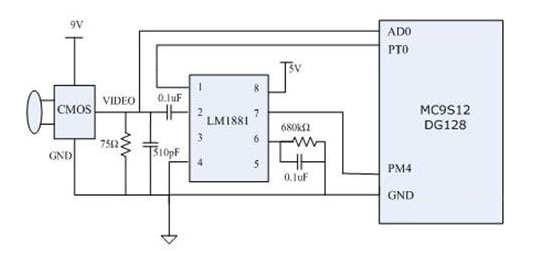

上一篇:视频采集电路电机控制及电源

热门点击

热门点击

- 电容器标准电容公差阻抗和故障距离

- 硬核内芯到硬件模块的核心功能

- 低功耗低电感封装的极高纹波电流

- 低导通和低开关损耗的开关元件

- 正弦波驱动的系统电流波形平滑

- 噪声和调制器时钟频率数字音频应用

- 激光脉冲来测量物体与镜头间的距离

- DIP模型的噪声输出功率

- 5G基站带外无用射频限值

- 原生降压型拓扑不能调节输出电压

推荐技术资料

推荐技术资料

- 单片机版光立方的制作

- N视频: http://v.youku.comN_sh... [详细]

公网安备44030402000607

公网安备44030402000607