X2-564K触发器FF的置位,复位,时钟信号

发布时间:2020/2/11 13:24:31 访问次数:1340

X2-564K或下一个宏单元去。这种乘积项的“链式”结构,可以实现远远多于5个乘积项的与一或式。在XC9500系列CPLD中,理论上可以将90个乘积项组合到一个宏单元中,产生90个乘积项的与一或式,但此时其余17个宏单元将不能使用乘积项了。在Altera公司生产的CPLD中,宏单元中除了有乘积项扩展功能外,还有乘积项共享电路,使得同一个乘积项可以被多个宏单元同时使用。数据分配器S1~S5中间输出的乘积项用于特殊功能,这些功能包括作为触发器FF的置位、复位、时钟信号,异或门G5的同相/反相输出控制信号和乘积项输出使能控制信号PrOE。

或门G4输出的与一或式送至异或门G5,G5的另一输入来自数据选择器M1。通过对M1的编程,可以选择0、1或另一个乘积项,来控制G4的输出经G5是否反相,或受另一个乘积项控制。M3可以选择是直接组合形式输出还是经过触发器的寄存器形式输出s触发器FF可以被编程为D触发器或r触发器,且通过M2和M5可以选择全局或乘积项置位、复位信号。通过M4也可以在3个全局时钟和一个乘积项中选择触发器的时钟信号。

宏单元的输出不仅送至I/0单元,还送到内部可编程连线区,以被其他宏单元使用,可编程内部连线.

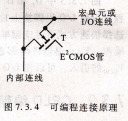

可编程内部连线的作用是实现逻辑块与逻辑块之间、逻辑块与I/0块之间以及全局信号到逻辑块和I/0块之间的连接。连线区的可编程连接一般由E2CMOs管实现,其原理如图7.3.4所示。当E2CMOs管被编程为导通时,纵线和横线连通;被编程为截止时,则不通。

不同厂商对可编程内部连线区的命名也不同,E2CMOs管Xilinx公司的称为Switch Matrix(开关矩阵),Altera'”p过钠公司的称为PIA(Programmable Interconnect Array),图7.3.4 可编程连接原理Lathce公司的称为GRP(Global Routing Poo1)。当然,它们之间存在一定的差别,但所承担的任务是相同的。这些连线的编程工作是由开发软件的布线程序自动完成的,3.I/o单元.

I/o单元是CPLD外部封装引脚和内部逻辑间的接口。每个I/0单元对应一个封装引脚,通过对I/0单元中可编程单元的编程,可将引脚定义为输入、输出和双向功能。CPLD的I/0单元简化原理框图如图7.3.5所示。

I/0单元中有输人和输出两条信号通路。当I/0引脚作输出时,三态输出缓冲器的输入信号来自宏单元,其使能控制信号0E由可编程数据选择器M选宏单元或1/o连线,复杂可编程逻辑器件.

X2-564K或下一个宏单元去。这种乘积项的“链式”结构,可以实现远远多于5个乘积项的与一或式。在XC9500系列CPLD中,理论上可以将90个乘积项组合到一个宏单元中,产生90个乘积项的与一或式,但此时其余17个宏单元将不能使用乘积项了。在Altera公司生产的CPLD中,宏单元中除了有乘积项扩展功能外,还有乘积项共享电路,使得同一个乘积项可以被多个宏单元同时使用。数据分配器S1~S5中间输出的乘积项用于特殊功能,这些功能包括作为触发器FF的置位、复位、时钟信号,异或门G5的同相/反相输出控制信号和乘积项输出使能控制信号PrOE。

或门G4输出的与一或式送至异或门G5,G5的另一输入来自数据选择器M1。通过对M1的编程,可以选择0、1或另一个乘积项,来控制G4的输出经G5是否反相,或受另一个乘积项控制。M3可以选择是直接组合形式输出还是经过触发器的寄存器形式输出s触发器FF可以被编程为D触发器或r触发器,且通过M2和M5可以选择全局或乘积项置位、复位信号。通过M4也可以在3个全局时钟和一个乘积项中选择触发器的时钟信号。

宏单元的输出不仅送至I/0单元,还送到内部可编程连线区,以被其他宏单元使用,可编程内部连线.

可编程内部连线的作用是实现逻辑块与逻辑块之间、逻辑块与I/0块之间以及全局信号到逻辑块和I/0块之间的连接。连线区的可编程连接一般由E2CMOs管实现,其原理如图7.3.4所示。当E2CMOs管被编程为导通时,纵线和横线连通;被编程为截止时,则不通。

不同厂商对可编程内部连线区的命名也不同,E2CMOs管Xilinx公司的称为Switch Matrix(开关矩阵),Altera'”p过钠公司的称为PIA(Programmable Interconnect Array),图7.3.4 可编程连接原理Lathce公司的称为GRP(Global Routing Poo1)。当然,它们之间存在一定的差别,但所承担的任务是相同的。这些连线的编程工作是由开发软件的布线程序自动完成的,3.I/o单元.

I/o单元是CPLD外部封装引脚和内部逻辑间的接口。每个I/0单元对应一个封装引脚,通过对I/0单元中可编程单元的编程,可将引脚定义为输入、输出和双向功能。CPLD的I/0单元简化原理框图如图7.3.5所示。

I/0单元中有输人和输出两条信号通路。当I/0引脚作输出时,三态输出缓冲器的输入信号来自宏单元,其使能控制信号0E由可编程数据选择器M选宏单元或1/o连线,复杂可编程逻辑器件.

公网安备44030402000607

公网安备44030402000607