LP62S16256EU-70LLI TTL门的逻辑电平

发布时间:2019/10/25 21:52:53 访问次数:840

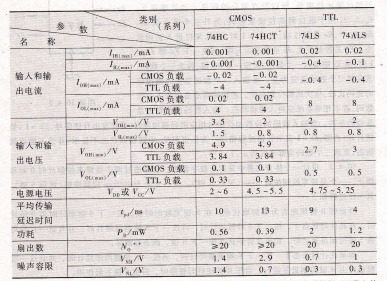

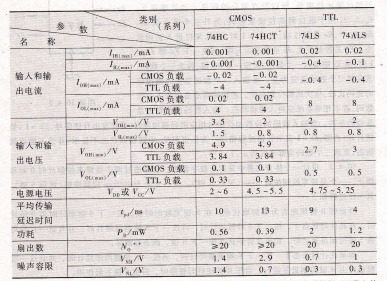

LP62S16256EU-70LLI本附录的参数参考Texas Instruments公司在可联网站上提供的集成电路产品数据,以及文献[3],测量条件为ycc=5Ⅴ,cL=15p「,Td=25℃=74 HC和74HCT的测试频率为1 MHz.~更详细的参数、可查阅有关器件的数据手册。

n0指带同类门的扇出数,如果保证CMOS驱动门的高电平输出为4,9V,74HC和74 HCT的n0为20。当允许其高电平输出降至TTL门的逻辑电平时,Ⅳ。4000,考虑CⅥ0S门的输人电容的影响,实际要比此数小:

Altera公司的Quartus Ⅱ软件主要用于开发该公司的FPGA和CPLD器件,它提供逻辑设计、综合、布局和布线、仿真验证、对器件编程等功能,可以替代该公司早期的MAX+Plus Ⅱ软件。目前Quartus Ⅱ 5.0软件是该公司2005年推出的最新版本。

安装Quadus Ⅱ 5.0版本的最低硬件配置为:奔腾Ⅱ400 MHz CPU,512 MB以上系统内存,大于1.2 GB安装该软件所需的最小硬盘空间。软件运行环境为: Windows NT4/2000/XP。

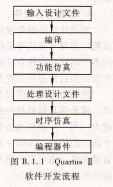

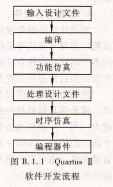

利用开发软件和编程工具对FPGA和CPLD器件进行设计开发的一般设计流程如图B.1,1所示,它包括设计准各、输人设计文件、处理设计文件、功能仿真、时序仿真、器件编程和实际测试等步骤。

设计准备,在设计一个数字电路或系统之前,设计者首先根据任务要求,例如系统的功能、复杂度、系统工作速度、成本等因素,选择合适的设计方案和合适的器件类型,然后采用自顶向下的方法对系统进行划分,并用适当的方式对系统的逻辑功能进行描述。

LP62S16256EU-70LLI本附录的参数参考Texas Instruments公司在可联网站上提供的集成电路产品数据,以及文献[3],测量条件为ycc=5Ⅴ,cL=15p「,Td=25℃=74 HC和74HCT的测试频率为1 MHz.~更详细的参数、可查阅有关器件的数据手册。

n0指带同类门的扇出数,如果保证CMOS驱动门的高电平输出为4,9V,74HC和74 HCT的n0为20。当允许其高电平输出降至TTL门的逻辑电平时,Ⅳ。4000,考虑CⅥ0S门的输人电容的影响,实际要比此数小:

Altera公司的Quartus Ⅱ软件主要用于开发该公司的FPGA和CPLD器件,它提供逻辑设计、综合、布局和布线、仿真验证、对器件编程等功能,可以替代该公司早期的MAX+Plus Ⅱ软件。目前Quartus Ⅱ 5.0软件是该公司2005年推出的最新版本。

安装Quadus Ⅱ 5.0版本的最低硬件配置为:奔腾Ⅱ400 MHz CPU,512 MB以上系统内存,大于1.2 GB安装该软件所需的最小硬盘空间。软件运行环境为: Windows NT4/2000/XP。

利用开发软件和编程工具对FPGA和CPLD器件进行设计开发的一般设计流程如图B.1,1所示,它包括设计准各、输人设计文件、处理设计文件、功能仿真、时序仿真、器件编程和实际测试等步骤。

设计准备,在设计一个数字电路或系统之前,设计者首先根据任务要求,例如系统的功能、复杂度、系统工作速度、成本等因素,选择合适的设计方案和合适的器件类型,然后采用自顶向下的方法对系统进行划分,并用适当的方式对系统的逻辑功能进行描述。

公网安备44030402000607

公网安备44030402000607