TAS5261DKDR 寄存器传输语言

发布时间:2019/10/25 21:17:52 访问次数:982

TAS5261DKDR第三部分定时器的HDL编写,可以根据ASM图或例10.3.1所示寄存器传输语言的描述进行。其工作过程由RESET和St控制。RESET信号使定时器清零后开始计数。st是由控制单元发出的信号,使定时器清零后重新计数。在SO、S2、S1(或S3)状态下,定时器分别给出3个定时信号Tl、Ts和Ty,以供控制单元决定是否进行状态转换。

第四部分输出电路的HDL是根据例10.3.1所示寄存器传输语言编写的。由case语句说明在不同的状态下,输出HG、HY、HR或FR、FY、FG中均有一个为1。

例10,4,1

∥交通灯控制系统的RTL描述

Inodule Traffic RTL(CLK,S,REsET,HG,HY,HR,FG,FY,FR);

/*=====定义输入/输出端口, 参见图10.2.6====*/

input CLK,S,RESET;

output HG,HY,HR,FG,FY,FR;

reg HG,HY,HR,FG,FY,FR; ∥输出信号是寄存器类型

∥定义系统内部的信号变量及其类型, 见图10.2.6

reg [3:0]TimerH,TimerL; ∥用于定时器的寄存器

wire T1,Ts,Ty;

reg st;

reg [1:0]CurrentState,NextState; ∥控制寄存器

∥对状态进行编码

paranleter SO=2i b00,S1 =2i b01,S2=2’b11,S3=2’b10;

/米=====控制单元状态转换的描述, 参见图10.2.8=====*/

always@(posedge CLK or negedge RESET)

begin.:statereg

if(~RESET) CurrentState(=SO; ∥初始sO状态

else (3urrentstate <=Nextstate;

end∥statereg

always@(S or Currentstate or Tl or Ts or Ty)

begin:fsm

case(CurrentState)

SO:begin

NextState=(Tl&&S)?S1:sO;

st=(Tl&&S)?1:0;

end

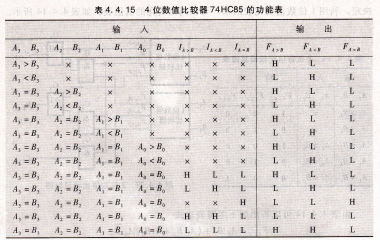

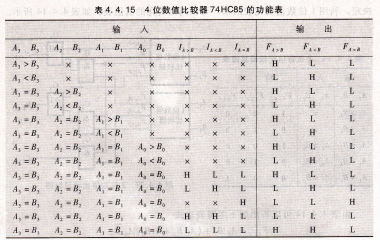

比较器的比较原理和2位比较器的比较原理相同。两个4位数的比较是从A的最高位A3和B的最高位B3进行比较,如果它们不相等,则该位的比较结果可以作为两数的比较结果。若最高位A3=B3,则再比较次高位A2和B2,以此类推。显然,如果两数相等,那么,必须将比较进行到最低位才能得到结果。若仅对4位数进行比较时,应对进行适当处理.

数值比较器的位数扩展,下面讨论数值比较器的位数扩展问题。数值比较器的扩展方式有串联和并联两种。图4.4.28所示为两个4位数值比较器串联而成为一个8位的数值比较器。对于两个8位数,若高4位相同,它们的大小则由低4位的比较结果确定。因此,低4位的比较结果应作为高4位的条件,即低4位比较器的输出端应分别与高4位比较器的二众端连接。

当位数较多且要满足一定的速度要求时,可以采取并联方式。图4,4.29所示为16位并联数值比较器的原理图。由图可以看出这里采用两级比较方法,将16位按高低位次序分成四组,每组4位,各组的比较是并行进行的。将每组的比较结果再经4位比较器进行比较后得出结果。显然,从数据输人到稳定输出只需2倍的4位比较器延迟时间,若用串联方式,则16位的数值比较器从输入到稳定输出需要约4倍的4位比较器的延迟时间。

TAS5261DKDR第三部分定时器的HDL编写,可以根据ASM图或例10.3.1所示寄存器传输语言的描述进行。其工作过程由RESET和St控制。RESET信号使定时器清零后开始计数。st是由控制单元发出的信号,使定时器清零后重新计数。在SO、S2、S1(或S3)状态下,定时器分别给出3个定时信号Tl、Ts和Ty,以供控制单元决定是否进行状态转换。

第四部分输出电路的HDL是根据例10.3.1所示寄存器传输语言编写的。由case语句说明在不同的状态下,输出HG、HY、HR或FR、FY、FG中均有一个为1。

例10,4,1

∥交通灯控制系统的RTL描述

Inodule Traffic RTL(CLK,S,REsET,HG,HY,HR,FG,FY,FR);

/*=====定义输入/输出端口, 参见图10.2.6====*/

input CLK,S,RESET;

output HG,HY,HR,FG,FY,FR;

reg HG,HY,HR,FG,FY,FR; ∥输出信号是寄存器类型

∥定义系统内部的信号变量及其类型, 见图10.2.6

reg [3:0]TimerH,TimerL; ∥用于定时器的寄存器

wire T1,Ts,Ty;

reg st;

reg [1:0]CurrentState,NextState; ∥控制寄存器

∥对状态进行编码

paranleter SO=2i b00,S1 =2i b01,S2=2’b11,S3=2’b10;

/米=====控制单元状态转换的描述, 参见图10.2.8=====*/

always@(posedge CLK or negedge RESET)

begin.:statereg

if(~RESET) CurrentState(=SO; ∥初始sO状态

else (3urrentstate <=Nextstate;

end∥statereg

always@(S or Currentstate or Tl or Ts or Ty)

begin:fsm

case(CurrentState)

SO:begin

NextState=(Tl&&S)?S1:sO;

st=(Tl&&S)?1:0;

end

比较器的比较原理和2位比较器的比较原理相同。两个4位数的比较是从A的最高位A3和B的最高位B3进行比较,如果它们不相等,则该位的比较结果可以作为两数的比较结果。若最高位A3=B3,则再比较次高位A2和B2,以此类推。显然,如果两数相等,那么,必须将比较进行到最低位才能得到结果。若仅对4位数进行比较时,应对进行适当处理.

数值比较器的位数扩展,下面讨论数值比较器的位数扩展问题。数值比较器的扩展方式有串联和并联两种。图4.4.28所示为两个4位数值比较器串联而成为一个8位的数值比较器。对于两个8位数,若高4位相同,它们的大小则由低4位的比较结果确定。因此,低4位的比较结果应作为高4位的条件,即低4位比较器的输出端应分别与高4位比较器的二众端连接。

当位数较多且要满足一定的速度要求时,可以采取并联方式。图4,4.29所示为16位并联数值比较器的原理图。由图可以看出这里采用两级比较方法,将16位按高低位次序分成四组,每组4位,各组的比较是并行进行的。将每组的比较结果再经4位比较器进行比较后得出结果。显然,从数据输人到稳定输出只需2倍的4位比较器延迟时间,若用串联方式,则16位的数值比较器从输入到稳定输出需要约4倍的4位比较器的延迟时间。

公网安备44030402000607

公网安备44030402000607