ULN2003ANE4结构控制字

发布时间:2019/10/24 12:23:44 访问次数:807

ULN2003ANE4反馈数据选择器FMUX,用于决定反馈信号的来源。根据控制信号ACO、处C1(刀)和AC1(而)的值,分别选择来自4路的不同信号反馈到与阵列的输人端。这4路信号是:地、相邻0LMC的输出、本级OLMC输出和本级D触发器的输出口。AC1(m)中的m表示相邻0LMC对应的0引脚号。

输出数据选择器OMUX,用于控制输出信号的来源。当控制信号AC0和AC1(屁)满足ACO+AC1(n)=0时,异或门的输出信号直接送达输出缓冲器;

但当ACO+AC1(n)=1时,D触发器的Q端信号送到输出缓冲器。

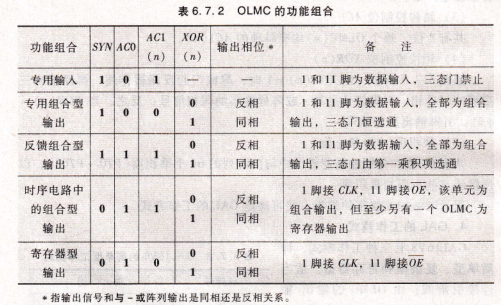

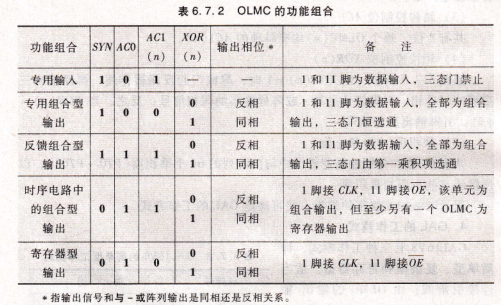

表6.7.2综合列出,在结构控制字同步位syⅣ、控制位ACO和AC1(n)的控制下,将OLMC设置成的5种不同功能组合。

结构控制字,GAL16V8的各种配置是由结构控制字来控制的。结构控制字如图6.7.4所示 。图中XOR(乃)和AC1(尼)字段下面的数字为乃值 ,表示它们控制的0LMC编号 ,与输出的引脚号一致 。

结构控制字各位功能如下:同步位syⅣ,该位用以确定GAL器件具有组合型输能力还是寄存器型输出能力。当syⅣ=1时 ,仅具有组合型输出能力;当syⅣ=o时,可具有寄存器型输出能力。此外,对于GAL16V8中的0LMC(12)和0LMC(19),syⅣ代替AC0,SyⅣ代替AC1(m)作为FMUX的输人信号。

时序可编程逻辑器件功能组合各注,专用输人1和11脚为数据输人,三态门禁止专用组合型输出反馈组合型输出时序电路中的组合型输出1和11脚为数据输人,全部为组合输出,三态门恒选通1和11脚为数据输人,全部为组合输出,二态门由第一乘积项选通1脚接CLK,11脚接@刀,该单元为组合输出,但至少另有一个0LMC为寄存器输出寄存器型输出1脚接CLK,11脚接OEAC0^C1Xr,R(n)输出相位来syⅣ0n.相相反同本目同相.

简化的IOB原理框图作。其最短延迟时间为零。

3个触发器均可编程配置为边沿触发或电平触发方式,它们共用一个时钟信号CLK,但有各自的时钟使能控制信号。通过它们可以实现同步输入/输出。输入、输出缓冲器和IOB中所有的信号,均有独立的极性控制电路(图7.4.8中未画出),可以控制信号是否反相,使能信号是高有效还是低有效,触发器是上升沿触发还是下降沿触发等。

图7.4,8中两个钳位二极管具有瞬时过压保护和静电保护作用。上拉电阻、下拉电阻和弱保持电路(Weakˉkeeper Circuit)可通过编程配置给I/o引脚。

弱保持电路监视并跟踪1/0引脚输入电压的变化,当连至引脚总线上所有的驱动信号全部无效时,弱保持电路将维持在引脚最后一个状态的逻辑电平上,可以避免总线处于悬浮状态,消除总线抖动。

为使FPGA能在不同电源系统中正常工作,IOB中设计了两个电压输入端Vcc。和ⅤRm(它们由多个IOB共用)。VRⅢ为逻辑电平的参考电压,在执行某些I/0标准时,需要输人ⅤREF①。大约每6个I/o有一个VREF引脚。

在此基础上,为了增强FPGA的适应性和灵活性,将若干个IOB组织在一起,构成一个组(Bank),如图7.4,9所示。一般FPGA的I/o划分为8个.

ULN2003ANE4反馈数据选择器FMUX,用于决定反馈信号的来源。根据控制信号ACO、处C1(刀)和AC1(而)的值,分别选择来自4路的不同信号反馈到与阵列的输人端。这4路信号是:地、相邻0LMC的输出、本级OLMC输出和本级D触发器的输出口。AC1(m)中的m表示相邻0LMC对应的0引脚号。

输出数据选择器OMUX,用于控制输出信号的来源。当控制信号AC0和AC1(屁)满足ACO+AC1(n)=0时,异或门的输出信号直接送达输出缓冲器;

但当ACO+AC1(n)=1时,D触发器的Q端信号送到输出缓冲器。

表6.7.2综合列出,在结构控制字同步位syⅣ、控制位ACO和AC1(n)的控制下,将OLMC设置成的5种不同功能组合。

结构控制字,GAL16V8的各种配置是由结构控制字来控制的。结构控制字如图6.7.4所示 。图中XOR(乃)和AC1(尼)字段下面的数字为乃值 ,表示它们控制的0LMC编号 ,与输出的引脚号一致 。

结构控制字各位功能如下:同步位syⅣ,该位用以确定GAL器件具有组合型输能力还是寄存器型输出能力。当syⅣ=1时 ,仅具有组合型输出能力;当syⅣ=o时,可具有寄存器型输出能力。此外,对于GAL16V8中的0LMC(12)和0LMC(19),syⅣ代替AC0,SyⅣ代替AC1(m)作为FMUX的输人信号。

时序可编程逻辑器件功能组合各注,专用输人1和11脚为数据输人,三态门禁止专用组合型输出反馈组合型输出时序电路中的组合型输出1和11脚为数据输人,全部为组合输出,三态门恒选通1和11脚为数据输人,全部为组合输出,二态门由第一乘积项选通1脚接CLK,11脚接@刀,该单元为组合输出,但至少另有一个0LMC为寄存器输出寄存器型输出1脚接CLK,11脚接OEAC0^C1Xr,R(n)输出相位来syⅣ0n.相相反同本目同相.

简化的IOB原理框图作。其最短延迟时间为零。

3个触发器均可编程配置为边沿触发或电平触发方式,它们共用一个时钟信号CLK,但有各自的时钟使能控制信号。通过它们可以实现同步输入/输出。输入、输出缓冲器和IOB中所有的信号,均有独立的极性控制电路(图7.4.8中未画出),可以控制信号是否反相,使能信号是高有效还是低有效,触发器是上升沿触发还是下降沿触发等。

图7.4,8中两个钳位二极管具有瞬时过压保护和静电保护作用。上拉电阻、下拉电阻和弱保持电路(Weakˉkeeper Circuit)可通过编程配置给I/o引脚。

弱保持电路监视并跟踪1/0引脚输入电压的变化,当连至引脚总线上所有的驱动信号全部无效时,弱保持电路将维持在引脚最后一个状态的逻辑电平上,可以避免总线处于悬浮状态,消除总线抖动。

为使FPGA能在不同电源系统中正常工作,IOB中设计了两个电压输入端Vcc。和ⅤRm(它们由多个IOB共用)。VRⅢ为逻辑电平的参考电压,在执行某些I/0标准时,需要输人ⅤREF①。大约每6个I/o有一个VREF引脚。

在此基础上,为了增强FPGA的适应性和灵活性,将若干个IOB组织在一起,构成一个组(Bank),如图7.4,9所示。一般FPGA的I/o划分为8个.

公网安备44030402000607

公网安备44030402000607