ȥ������ǿ˷��������������һ�ַ���

����ʱ��:2019/1/10 21:43:25 ���ʴ���:871

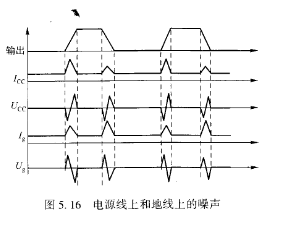

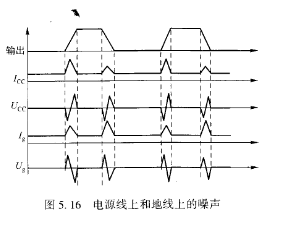

����,��״̬�����仯ʱ,����һ��ʱ��Q3��Q4ͬʱ��ͨ,��ʱ�ڵ�Դ���֮���γ����ݵĵ��迹,����30~100n1A�ļ�����[��������ӵͱ�Ϊ��ʱ, LFE2-70SE5FN676C��Դ�����ṩ��·�ĵ���,��Ҫ�����������ṩ���ĵ���.ʹ��������ķ�ֵ�������ڵ�Դ�������в�ͬ�̶ȵĵ��,���˵���������ͻ��ʱ�����и�Ӧ��ѹ,����ǵ�Դ���ϳ��ֵ�����������Դ���ϲ������ʱ,�����ϱ�ȻҲ�����������,���ڵ���Ҳ�ܻ��в�ͬ�̶ȵĵ��,���Ҳ���Ӧ����ѹ,��ͳ����˵�������,�ر��Ƕ������źŵĵ�·��˵,���������Ӽ���,��ͼ5.16��ʾ��

ȥ������ǿ˷��������������һ�ַ����������е��ź����Ź������������������ͬʱ����ʱ,ȥ����ݻ��ṩ��Ԫ����ʱ�Ӻ����ݱ仯�ڼ�������������Ķ�̬��ѹ�͵�����ȥ����ͨ�����ź��ߺ͵�Դƽ����ṩһ�����迹�ĵ�Դ��ʵ�ֵġ���Ƶ�����ߵ���г���֮ǰ,����Ƶ�ʵ����,ȥ����ݵ��迹��Խ��Խ��,����,��Ƶ��������Ч�ش��ź�����й��,��ʱ���µĵ�Ƶ��Ƶ������û��ʲôӰ���ˡ�

0.1uF���ݺ�0.01uF�����ǵ�����ٵ�·�������õ�ȥ����ݡ�һ��������������г���������ᳬ��500MHz,0.01uF�ı�������ݵ���г��������50~150MHz֮��,������ʵ�ʵ�PCBӦ����,���ߵ�С����ȵĴ��ڻ��һ������ȥ���·��г��㡣����ʹ�ò�����ȥ�����ѡ��ԽС,ȥ��Ƶ�ʾͻ������Ƶظߡ�ʵ��Ӧ�������ߵ�еĴ���ʹ��С�ĵ��ݵ�ȥ��Ƶ������Ҳ���ᳬ��300MHz����Ҳ�Ǻܶ��·�м�ʹ����Ƶ���ٸ�,��ȥ�������СҲֻ��0.01uF��ԭ������ͬ��ֵ�ĵ��ݲ���,���ߵ�кͼ�����в�������С,ʹ��������迹����½�����,��������ȥ����ݹ���Ƶ�ʵ����ߡ�������ֵ��ȥ������������ŵ�·��תʱ,��������ͬ��ʱ�����ṩ���������������,�ڶ��PCB�����������Դƽ��͵�ƽ����ɵİ�����,���ų���ESL���ص�,���Ǹ�Ƶ��·��Ƶ�Դȥ�����Ҫ�ֶΡ�

����,��״̬�����仯ʱ,����һ��ʱ��Q3��Q4ͬʱ��ͨ,��ʱ�ڵ�Դ���֮���γ����ݵĵ��迹,����30~100n1A�ļ�����[��������ӵͱ�Ϊ��ʱ, LFE2-70SE5FN676C��Դ�����ṩ��·�ĵ���,��Ҫ�����������ṩ���ĵ���.ʹ��������ķ�ֵ�������ڵ�Դ�������в�ͬ�̶ȵĵ��,���˵���������ͻ��ʱ�����и�Ӧ��ѹ,����ǵ�Դ���ϳ��ֵ�����������Դ���ϲ������ʱ,�����ϱ�ȻҲ�����������,���ڵ���Ҳ�ܻ��в�ͬ�̶ȵĵ��,���Ҳ���Ӧ����ѹ,��ͳ����˵�������,�ر��Ƕ������źŵĵ�·��˵,���������Ӽ���,��ͼ5.16��ʾ��

ȥ������ǿ˷��������������һ�ַ����������е��ź����Ź������������������ͬʱ����ʱ,ȥ����ݻ��ṩ��Ԫ����ʱ�Ӻ����ݱ仯�ڼ�������������Ķ�̬��ѹ�͵�����ȥ����ͨ�����ź��ߺ͵�Դƽ����ṩһ�����迹�ĵ�Դ��ʵ�ֵġ���Ƶ�����ߵ���г���֮ǰ,����Ƶ�ʵ����,ȥ����ݵ��迹��Խ��Խ��,����,��Ƶ��������Ч�ش��ź�����й��,��ʱ���µĵ�Ƶ��Ƶ������û��ʲôӰ���ˡ�

0.1uF���ݺ�0.01uF�����ǵ�����ٵ�·�������õ�ȥ����ݡ�һ��������������г���������ᳬ��500MHz,0.01uF�ı�������ݵ���г��������50~150MHz֮��,������ʵ�ʵ�PCBӦ����,���ߵ�С����ȵĴ��ڻ��һ������ȥ���·��г��㡣����ʹ�ò�����ȥ�����ѡ��ԽС,ȥ��Ƶ�ʾͻ������Ƶظߡ�ʵ��Ӧ�������ߵ�еĴ���ʹ��С�ĵ��ݵ�ȥ��Ƶ������Ҳ���ᳬ��300MHz����Ҳ�Ǻܶ��·�м�ʹ����Ƶ���ٸ�,��ȥ�������СҲֻ��0.01uF��ԭ������ͬ��ֵ�ĵ��ݲ���,���ߵ�кͼ�����в�������С,ʹ��������迹����½�����,��������ȥ����ݹ���Ƶ�ʵ����ߡ�������ֵ��ȥ������������ŵ�·��תʱ,��������ͬ��ʱ�����ṩ���������������,�ڶ��PCB�����������Դƽ��͵�ƽ����ɵİ�����,���ų���ESL���ص�,���Ǹ�Ƶ��·��Ƶ�Դȥ�����Ҫ�ֶΡ�

�������

�������

- PWM�źŲ���оƬ����KA3525A

- ��ԴƵ�ʵͶ��첽�綯����������ʲôӰ��?

- MLCT����ԾǨ����ȡ�����ؽ����Ĺ��������

- LDOоƬǰ�����ӵĶ����ܲ������赲��ӿ����

- �첽�綯�����ص���ռ��������Ϊ����?

- ѡ������ʱһ��Ҫע������������

- ����ʱ������оƬ�ĸ���ͨ������

- оƬ���������ϴ�����ȥ����ݵ�λ��

- FDS6982S̼ԭ���ӻ�ǰ��ĵ����Ų�

- ��ѹ�����ı仯ͨ�����ߴ���ʱ��������̬

�Ƽ���������

�Ƽ���������

- ����������ICL7135

- ��ͷʹff11CL7135��ΪADC��ICL7135��... [��ϸ]

��������44030402000607

��������44030402000607