串行接口

发布时间:2018/2/5 22:00:01 访问次数:466

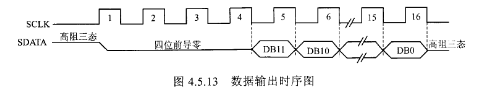

串行接口:AD7896采用三线接口方式向外输出转换结果:串行时钟输入(sCLK)、串行数据输出(sDATA)和转换状态输出①UsY)。它可以与多种微控制器、DsP、HZICCX1084T2520G移位寄存器等直接相连。AD78%的数据输出操作时序图如图45,13所示。时钟源有串行时钟(sCLK)端提供,在sCLK的下降沿后输出串行数据,上升沿数据输出有效,下一个sCLK的下降沿此位数据变为无效。这种从上升沿到下降沿之间数据输出有效的操作方式具有很大的灵活性。

图4513 数据输出时序图

由图4,5.13可知,输出12位转换数据需要16个串行时钟脉冲。起始4个脉冲输出前导零,以后读出来的依次是最高位(DB11),次高位①B10),……,最后的第16个时钟脉冲输出转换数据的最低位(DB0)。16个时钟脉冲后,SDATA输出高阻。此后sCLK应保持低电平,直到下一

次读周期开始。sCLK端在16个时钟输入后不应有额外时钟输入,否则AD7896将输出复位后输出寄存器的内容,SDATA不再是高阻。即使在串行输入时钟结束后,sDATA端仍不能恢复高阻,但不会影响下一次转换操作,因为CoNVsT下降沿将复位输出结果寄存器,准备下一次转换操作。但要正确复位输出寄存器,在Cα踽厂sT下降沿产生过程中,sCLK端必须保持低电平。输出转换结果数据并不要求串行时钟一定是连续的,整个16位数据(包括4位前导零)可分成字节方式输出,但要求2字节之间sCLK端应保持低电平。

AD7896是通过对时钟沿的计数决定将输出寄存器中哪一位数据放在sDATA端上。为同步见,以CONVsT下降沿复位串行时钟计数器,当然,SCLK端此时应保持低电平。所以取转换数据时,不应有COblVsT下降沿输入。

串行接口:AD7896采用三线接口方式向外输出转换结果:串行时钟输入(sCLK)、串行数据输出(sDATA)和转换状态输出①UsY)。它可以与多种微控制器、DsP、HZICCX1084T2520G移位寄存器等直接相连。AD78%的数据输出操作时序图如图45,13所示。时钟源有串行时钟(sCLK)端提供,在sCLK的下降沿后输出串行数据,上升沿数据输出有效,下一个sCLK的下降沿此位数据变为无效。这种从上升沿到下降沿之间数据输出有效的操作方式具有很大的灵活性。

图4513 数据输出时序图

由图4,5.13可知,输出12位转换数据需要16个串行时钟脉冲。起始4个脉冲输出前导零,以后读出来的依次是最高位(DB11),次高位①B10),……,最后的第16个时钟脉冲输出转换数据的最低位(DB0)。16个时钟脉冲后,SDATA输出高阻。此后sCLK应保持低电平,直到下一

次读周期开始。sCLK端在16个时钟输入后不应有额外时钟输入,否则AD7896将输出复位后输出寄存器的内容,SDATA不再是高阻。即使在串行输入时钟结束后,sDATA端仍不能恢复高阻,但不会影响下一次转换操作,因为CoNVsT下降沿将复位输出结果寄存器,准备下一次转换操作。但要正确复位输出寄存器,在Cα踽厂sT下降沿产生过程中,sCLK端必须保持低电平。输出转换结果数据并不要求串行时钟一定是连续的,整个16位数据(包括4位前导零)可分成字节方式输出,但要求2字节之间sCLK端应保持低电平。

AD7896是通过对时钟沿的计数决定将输出寄存器中哪一位数据放在sDATA端上。为同步见,以CONVsT下降沿复位串行时钟计数器,当然,SCLK端此时应保持低电平。所以取转换数据时,不应有COblVsT下降沿输入。

上一篇:AD7896提供两种工作方式

上一篇:典型应用

热门点击

热门点击

- DAC的性能指标

- 施密特触发器在波形变换、整形等方面的基本应用

- 用锁相环构成FM解调器

- 二次击穿现象

- DAC的选择要点

- 关断增益

- 大惯性负载变频器的选择

- 常用光电耦合器的选择及其驱动电路

- 电容器的主要失效模式

- 当MOSFET的器件尺寸缩得非常小

推荐技术资料

推荐技术资料

- 中国传媒大学传媒博物馆开

- 传媒博物馆开馆仪式隆童举行。教育都i国家广电总局等部门... [详细]

公网安备44030402000607

公网安备44030402000607