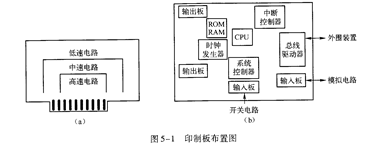

印制板布置图

发布时间:2017/3/5 19:21:11 访问次数:426

如图5-1(b)所示,以核心元器件(此处为CPU)为中心进行元器件布局,

围绕核心元器件布置与核心元器件相关的其他元器件。 ESD5325E-6/TR应把相互有关的元器件尽量放得靠近些,这样可以获得较好的EMC特性。元器件在印制电路板上排列的位置要保证各元器件之间的高频、高速连线及敏感信号连线尽量短。在布局上,要把模拟电路部分、高速数字电路部分、噪声源电路部分(如继电器、大电流开关等)这三部分合理地分开,使相互间的信号耦合最小。时钟发生器、晶振和CPU的时钟输人端都易对外发射骚扰,三者要尽量相互靠近以尽量减小时钟信号环路面积,从而有效减少对外发射骚扰。易产生骚扰的元器件、大电流电路、功率电路、电源电路、数字逻辑电路等应尽量远离低频小信号模拟电路。如有可能,敏感的低频小信号模拟电路应另做电路板,这一点十分重要。

尽可能缩短高频元器件之间的连线,设法减少它们的分布参数和相互间的电磁串扰。易受干扰的元器件之间不能相互挨得太近,输人和输出元器件应尽量远离。某些元器件或导线之间可能有较高的电位差,应加大它们之间的距离,以免过压击穿引发意外短路和元器件损毁。带高电压的元器件应尽量布置在调试时手不易触及的地方,防止危及人身安全。

如图5-1(b)所示,以核心元器件(此处为CPU)为中心进行元器件布局,

围绕核心元器件布置与核心元器件相关的其他元器件。 ESD5325E-6/TR应把相互有关的元器件尽量放得靠近些,这样可以获得较好的EMC特性。元器件在印制电路板上排列的位置要保证各元器件之间的高频、高速连线及敏感信号连线尽量短。在布局上,要把模拟电路部分、高速数字电路部分、噪声源电路部分(如继电器、大电流开关等)这三部分合理地分开,使相互间的信号耦合最小。时钟发生器、晶振和CPU的时钟输人端都易对外发射骚扰,三者要尽量相互靠近以尽量减小时钟信号环路面积,从而有效减少对外发射骚扰。易产生骚扰的元器件、大电流电路、功率电路、电源电路、数字逻辑电路等应尽量远离低频小信号模拟电路。如有可能,敏感的低频小信号模拟电路应另做电路板,这一点十分重要。

尽可能缩短高频元器件之间的连线,设法减少它们的分布参数和相互间的电磁串扰。易受干扰的元器件之间不能相互挨得太近,输人和输出元器件应尽量远离。某些元器件或导线之间可能有较高的电位差,应加大它们之间的距离,以免过压击穿引发意外短路和元器件损毁。带高电压的元器件应尽量布置在调试时手不易触及的地方,防止危及人身安全。

上一篇:元器件布局原则

热门点击

热门点击

公网安备44030402000607

公网安备44030402000607