薄膜淀积

发布时间:2015/11/6 19:32:44 访问次数:477

虽然掺杂的Ⅸ域和PN结形成电路中的电子有源元件的核心,但是需要各种其他半导体、 AD7548SQ/883绝缘介质和导电层完成器件,并促使这些器件集成为电路。有几种技术可以将这些层加到晶圆的表面,j莺要一螳是化学气相淀积(CVD)、物理气相淀积(PVD)、电镀、旋转涂敷和蒸发。本章将描述最常用的CVD技术和淀积在晶圆表面的半导体材料。PVD、电镀、旋转涂敷和蒸发工艺将存第13章描述。

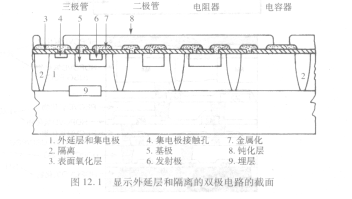

光刻掩膜技术的进步已经促进了甚大规模集成电路( ULSI)的制造。随着电路尺寸的不断缩小,也开始通过增加淀积层数的方法,在垂直方向上进行拓展。在20世纪60年代,双极器件已经采用r化学气相淀积技术完成的双层结构,即外延层和顶部的二氧化硅钝化层(见图12.1),而早期的MOS器件仅有一层钝化层(见图12.2)。到20世纪90年代,先进的MOS器件具有4层金属内部连接,需要许多淀积层。这“堆叠”已经伴随更多金属层、器件方

案和绝缘层,专rJ的金属化技术将在第13章论述。通用器件结构将在第17章论述。

虽然掺杂的Ⅸ域和PN结形成电路中的电子有源元件的核心,但是需要各种其他半导体、 AD7548SQ/883绝缘介质和导电层完成器件,并促使这些器件集成为电路。有几种技术可以将这些层加到晶圆的表面,j莺要一螳是化学气相淀积(CVD)、物理气相淀积(PVD)、电镀、旋转涂敷和蒸发。本章将描述最常用的CVD技术和淀积在晶圆表面的半导体材料。PVD、电镀、旋转涂敷和蒸发工艺将存第13章描述。

光刻掩膜技术的进步已经促进了甚大规模集成电路( ULSI)的制造。随着电路尺寸的不断缩小,也开始通过增加淀积层数的方法,在垂直方向上进行拓展。在20世纪60年代,双极器件已经采用r化学气相淀积技术完成的双层结构,即外延层和顶部的二氧化硅钝化层(见图12.1),而早期的MOS器件仅有一层钝化层(见图12.2)。到20世纪90年代,先进的MOS器件具有4层金属内部连接,需要许多淀积层。这“堆叠”已经伴随更多金属层、器件方

案和绝缘层,专rJ的金属化技术将在第13章论述。通用器件结构将在第17章论述。

热门点击

热门点击

- 芯片和晶圆尺寸的增大

- 双大马士革铜工艺

- 电缆各支持点间的距离

- PE线的重复接地可以降低当相线碰壳短路时的设

- 四探针测试仪测量厚度

- 电压损失是指线路始端电压与末端电压的代数差

- TT系统内的漏电保护器

- 硅湿法刻蚀

- TN-C方式供电系统是用工作零线兼作接零保护

- 退火和杂质激活

推荐技术资料

推荐技术资料

- 硬盘式MP3播放器终级改

- 一次偶然的机会我结识了NE0 2511,那是一个远方的... [详细]

公网安备44030402000607

公网安备44030402000607