CMOS或门

发布时间:2015/8/18 21:13:23 访问次数:2502

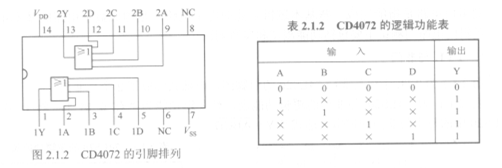

图2 .1.2为CMOS或门CD4072的引脚图,FDMA420NZ内部共集成了2个或门。

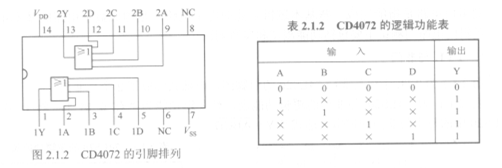

表2 .1.2为CD4072或门的逻辑功能表,其逻辑功能为“有l出1,全0出0”。CD4072中的每个或门的逻辑表达式是Y= A+B+C+D。

图2.1.2 CD4072的引脚排列

表2.1.2 CD4072酌逻辑功能表

CMOS门电路的主要参数定义及测试方法与TTL电路相仿。CMOS的电压传输特性接近于理想的开关特性,曲线转折区非常窄,因此直流噪声容限较高。当电源电压VDD为SV时,标准4000系列CMOS电路的噪声容限最小值为1V。另外对CMOS电路而言,电源电压越高,直流噪声容限越大。CMOS电路输入阻抗高,输出阻抗低,因此扇出系数很大。

图2 .1.2为CMOS或门CD4072的引脚图,FDMA420NZ内部共集成了2个或门。

表2 .1.2为CD4072或门的逻辑功能表,其逻辑功能为“有l出1,全0出0”。CD4072中的每个或门的逻辑表达式是Y= A+B+C+D。

图2.1.2 CD4072的引脚排列

表2.1.2 CD4072酌逻辑功能表

CMOS门电路的主要参数定义及测试方法与TTL电路相仿。CMOS的电压传输特性接近于理想的开关特性,曲线转折区非常窄,因此直流噪声容限较高。当电源电压VDD为SV时,标准4000系列CMOS电路的噪声容限最小值为1V。另外对CMOS电路而言,电源电压越高,直流噪声容限越大。CMOS电路输入阻抗高,输出阻抗低,因此扇出系数很大。

上一篇:74LS20的引脚排列

上一篇:本实验所用电源均为SV

公网安备44030402000607

公网安备44030402000607