抵消环路

发布时间:2014/4/18 21:22:31 访问次数:416

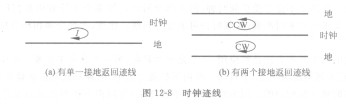

如果我们不能印制足够小的环路,我们可HEF4081BP以找到一个简单的方法去印制两个相互抵消的环路吗?考虑如图12-8(a)所示的一个时钟迹线和它的接地返回路径的情况。来自环路的发射将是环路面积和环路中电流的函数。如果这表示作为PCB技术可以印制的最靠近的迹线,则除了屏蔽PCB,我们不能减小发射。

然而,考虑如图12-8(b)所示的布线。这里,我们有一个时钟迹线,在这个时钟迹线两边各有一个接地返回迹线。因此,我们有两个环路,每个都与图12-8 (a)所示的环路有相同的面积。如果两个返回(接地)迹线相对时钾迹线对称分布,则返回电流将在两个路径中分流。因此,图12-8(b)中下面的环路将只有图12-8(a)中环路电流的一半,而且将只辐射一半或减少6dB。

当然,另一半是图12-8 (b)上面的环路辐射,而且它将与下面的环路辐射的一样多。然而,注意到上面环路中的电流是逆时针流动的,而下面环路中的电流是顺时针流动的。因此,来自上面环路中的辐射与来自下面环路中的辐射不是相加,而是相抵消。抵消将不完全,但非常好。图12-8(b)中的布线因此将比图12-8(a)中的辐射减少20dB。

图12-8中所示的迹线可被看成是印制在PCB的同一层或不同层上。后面的例子将介绍一个印制在位于两个接地层中间的一个PCB层上的时钟。

如果我们不能印制足够小的环路,我们可HEF4081BP以找到一个简单的方法去印制两个相互抵消的环路吗?考虑如图12-8(a)所示的一个时钟迹线和它的接地返回路径的情况。来自环路的发射将是环路面积和环路中电流的函数。如果这表示作为PCB技术可以印制的最靠近的迹线,则除了屏蔽PCB,我们不能减小发射。

然而,考虑如图12-8(b)所示的布线。这里,我们有一个时钟迹线,在这个时钟迹线两边各有一个接地返回迹线。因此,我们有两个环路,每个都与图12-8 (a)所示的环路有相同的面积。如果两个返回(接地)迹线相对时钾迹线对称分布,则返回电流将在两个路径中分流。因此,图12-8(b)中下面的环路将只有图12-8(a)中环路电流的一半,而且将只辐射一半或减少6dB。

当然,另一半是图12-8 (b)上面的环路辐射,而且它将与下面的环路辐射的一样多。然而,注意到上面环路中的电流是逆时针流动的,而下面环路中的电流是顺时针流动的。因此,来自上面环路中的辐射与来自下面环路中的辐射不是相加,而是相抵消。抵消将不完全,但非常好。图12-8(b)中的布线因此将比图12-8(a)中的辐射减少20dB。

图12-8中所示的迹线可被看成是印制在PCB的同一层或不同层上。后面的例子将介绍一个印制在位于两个接地层中间的一个PCB层上的时钟。

上一篇:时钟信号应首先在PCB上布线

上一篇:抖动时钟

公网安备44030402000607

公网安备44030402000607