测试并验证逻辑功能

发布时间:2014/2/15 19:23:39 访问次数:1585

操作方法与说明:

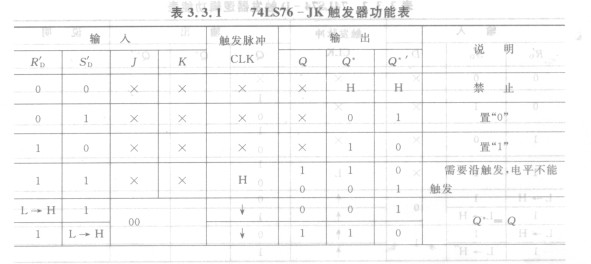

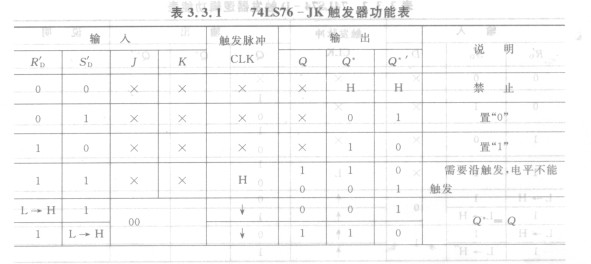

(1)J,K,RtD,StD接电平给定开关插孔,Q接电平显示插孑L,CLK接单脉冲插孑L,NLV32T-820J-PF按功能表(见表3.3.1)测试并验证逻辑功能。

(2)R乞是给输出Q置“0”的,S,D是给输出Q置“1”的,均为低电平有效。

(3)RD和S;)可以同为高电平,表示不置数。R:和S:不能同为低电平,既置“o”又置“1”,这是禁止的。

(4)Q’是触发器被触发后的Q端状态。

(5)当RD是低电平时,输出Q被置为“0”,其操作L一H表示用低电平给输出置“0”后必须回到高电平,触发器才能被触发,否则输出将被锁定在“O”状态。同样,当S;)是低电平时,输出Q被置为“1”,其操作L―H表示用低电平给输出置“1”后必须回到高电平,触发器才能被触发,否则输出将被锁定在“1”状态。

验证D触发器的逻辑功能

方法同JK触发器功能验证。

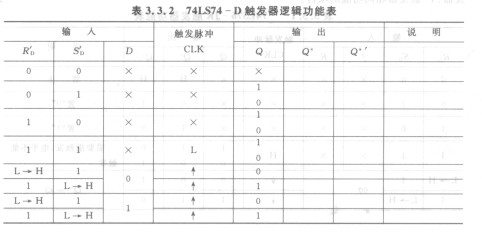

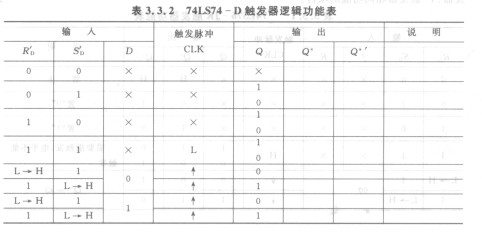

要求:按照表3.3.2完成功能表Q*的测试,总结功能,填注说明。

表3.3.2 74LS74 -D觖发器逻辑功能表

操作方法与说明:

(1)J,K,RtD,StD接电平给定开关插孔,Q接电平显示插孑L,CLK接单脉冲插孑L,NLV32T-820J-PF按功能表(见表3.3.1)测试并验证逻辑功能。

(2)R乞是给输出Q置“0”的,S,D是给输出Q置“1”的,均为低电平有效。

(3)RD和S;)可以同为高电平,表示不置数。R:和S:不能同为低电平,既置“o”又置“1”,这是禁止的。

(4)Q’是触发器被触发后的Q端状态。

(5)当RD是低电平时,输出Q被置为“0”,其操作L一H表示用低电平给输出置“0”后必须回到高电平,触发器才能被触发,否则输出将被锁定在“O”状态。同样,当S;)是低电平时,输出Q被置为“1”,其操作L―H表示用低电平给输出置“1”后必须回到高电平,触发器才能被触发,否则输出将被锁定在“1”状态。

验证D触发器的逻辑功能

方法同JK触发器功能验证。

要求:按照表3.3.2完成功能表Q*的测试,总结功能,填注说明。

表3.3.2 74LS74 -D觖发器逻辑功能表

上一篇:实验仪器及材料

上一篇:将JK触发器转换成D触发器

热门点击

热门点击

- 74LS90的功能表

- 不同颜色的发光二极管所采用的基本材料及工作电

- “Routing Via Style”过孔类

- 五色环电阻器的读数方法

- 用555定时器组成施密特触发

- RS触发器

- 高通滤波器

- 测试并验证逻辑功能

- 整流二极管

- 总结示波器测量电压和频率的方法

推荐技术资料

推荐技术资料

- 单片机版光立方的制作

- N视频: http://v.youku.comN_sh... [详细]

公网安备44030402000607

公网安备44030402000607