低噪声高输入阻抗放大电路

发布时间:2012/8/19 20:51:08 访问次数:2661

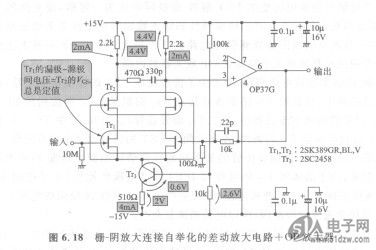

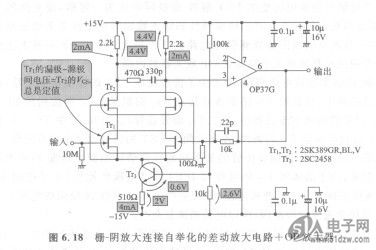

图6.18是栅一阴放大连接TLC7226CN自举化的N沟JFET差动放大电路与OP放大器组合的低噪声高输入阻抗放大电路。

差动放大电路也能够栅一阴放大连接自举化。如图6.18所示,在连接OP放大器加负反馈时,由于栅一阴放大连接自举化使差动放大电路的频率特性得到改善,电路的工作稳定,相位补偿也变得容易。

使用JFET使差动放大电路栅一阴放大连接自举化时应该注意的是,不只是差动放大的输入部分采用单片双器件,作为栅极接地工作的上侧的JFET(参见图6. 18的Trz)也要采用单片双FET器件。

否则的话,由于差动输入部分FET的漏极一源极间电压出现了大的差值(栅极接地部分使用的两个FET的VGS差值原封不动地变成差动输入部分漏极一源极间电压的差值),差动输入部分的输入电容CiSS出现了大的差值,在高频范围CMRR(共态抑制比,表征能够在多大程度上排除加到两个输入端上的同一信号成分的特性)将变坏。

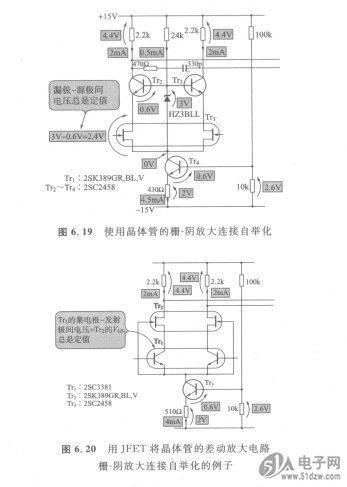

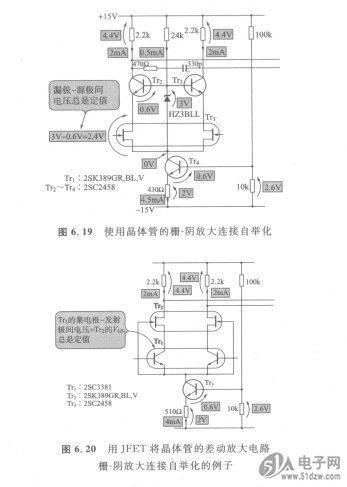

当然,如图6. 9所示,使用晶体管的基极接地也能够使差动放大电路栅一阴放大连接自举化。不过如图6. 17所说明的那样,偏置电路将变得复杂化。

图6.18是栅一阴放大连接TLC7226CN自举化的N沟JFET差动放大电路与OP放大器组合的低噪声高输入阻抗放大电路。

差动放大电路也能够栅一阴放大连接自举化。如图6.18所示,在连接OP放大器加负反馈时,由于栅一阴放大连接自举化使差动放大电路的频率特性得到改善,电路的工作稳定,相位补偿也变得容易。

使用JFET使差动放大电路栅一阴放大连接自举化时应该注意的是,不只是差动放大的输入部分采用单片双器件,作为栅极接地工作的上侧的JFET(参见图6. 18的Trz)也要采用单片双FET器件。

否则的话,由于差动输入部分FET的漏极一源极间电压出现了大的差值(栅极接地部分使用的两个FET的VGS差值原封不动地变成差动输入部分漏极一源极间电压的差值),差动输入部分的输入电容CiSS出现了大的差值,在高频范围CMRR(共态抑制比,表征能够在多大程度上排除加到两个输入端上的同一信号成分的特性)将变坏。

当然,如图6. 9所示,使用晶体管的基极接地也能够使差动放大电路栅一阴放大连接自举化。不过如图6. 17所说明的那样,偏置电路将变得复杂化。

上一篇:棚一阴放大连接自举电路

上一篇:电流反馈型OP放大器的设计与制作

公网安备44030402000607

公网安备44030402000607