Blackfin处理器的时钟频率控制

发布时间:2012/2/21 19:33:39 访问次数:2221

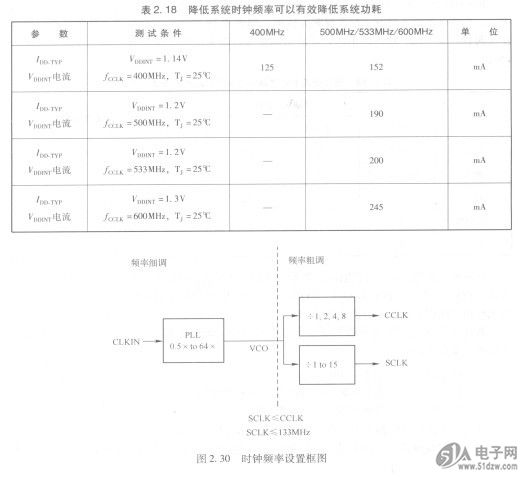

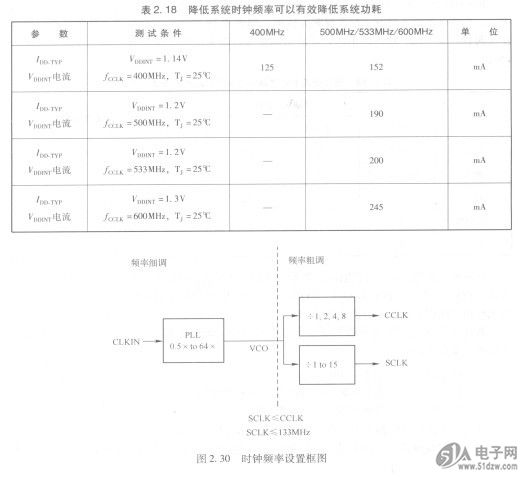

如表2. 18所示,在Blackfin处理器中,降低系统时钟频率可以有效降低系统功耗。例如,Blackfin处理器ADSP- BF533通过外部时钟输入引脚CLKIN接收外部时钟源(10~40MHz)的时钟输入,再通过锁相环( PLL),电路模块产生内核时钟(CCLK)和系统时钟(SCLK),通过设置PLL相关寄存器实现对CCLK和SCLK的频率控制‘拇1。时钟频率设置框图如图2.30所示。CGY

CCLK和SCLK均由VCO(压控振荡器)输出的时钟分频后得到。VCO输出时钟频率由PI_,L控制寄存器(PLL_CTL)设置,CCLK和SCLK对VCO的分频因子由PLL分频寄存器( PLL_DIV)设置。需要注意的是,VCO最小输出时钟频率为50MHz,最大输出频率为内核时钟CCLK频率的最大值。对于ADSP- BF533,CCLK最大值为600MHz,而ADSP- BF532 /531的CCLK最大值为400MHz。所以VCO输出频率不应超出50MHz~CCLK。

用户可以通过设置PLL分频寄存器PLL_DIV中的CSEL(PLL_DIV的4~5位)确定CCLK,通过设置SSEL(PLL_DIV的0~3位)确定SCLK。

由于SCLK频率不能高于CCLK的频率,所以在对SSEL参数设置时,需要确定当前CCLK的频率。假设外部时钟输入CLKIN=27MHz,将CCLK设置为594MHz (27×22),SCLK设置为11818MHz (594 /5)。

如表2. 18所示,在Blackfin处理器中,降低系统时钟频率可以有效降低系统功耗。例如,Blackfin处理器ADSP- BF533通过外部时钟输入引脚CLKIN接收外部时钟源(10~40MHz)的时钟输入,再通过锁相环( PLL),电路模块产生内核时钟(CCLK)和系统时钟(SCLK),通过设置PLL相关寄存器实现对CCLK和SCLK的频率控制‘拇1。时钟频率设置框图如图2.30所示。CGY

CCLK和SCLK均由VCO(压控振荡器)输出的时钟分频后得到。VCO输出时钟频率由PI_,L控制寄存器(PLL_CTL)设置,CCLK和SCLK对VCO的分频因子由PLL分频寄存器( PLL_DIV)设置。需要注意的是,VCO最小输出时钟频率为50MHz,最大输出频率为内核时钟CCLK频率的最大值。对于ADSP- BF533,CCLK最大值为600MHz,而ADSP- BF532 /531的CCLK最大值为400MHz。所以VCO输出频率不应超出50MHz~CCLK。

用户可以通过设置PLL分频寄存器PLL_DIV中的CSEL(PLL_DIV的4~5位)确定CCLK,通过设置SSEL(PLL_DIV的0~3位)确定SCLK。

由于SCLK频率不能高于CCLK的频率,所以在对SSEL参数设置时,需要确定当前CCLK的频率。假设外部时钟输入CLKIN=27MHz,将CCLK设置为594MHz (27×22),SCLK设置为11818MHz (594 /5)。

公网安备44030402000607

公网安备44030402000607