D触发器

发布时间:2012/2/15 21:40:30 访问次数:5101

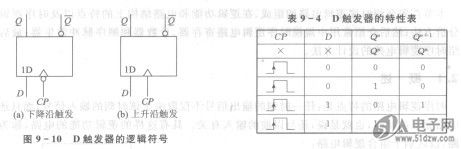

边沿D触发器逻辑电路符号如图9 -10所示。D触发器特性表如表9-4所列。D触发器具有在时钟脉冲上升沿(或下降沿)触发的特点,当时钟脉冲上升沿或下降沿时刻,输入端D的值传输到输出端,也就是说输出端Q的状态随着输入端D的值变化,即时钟脉冲来到之后Q的状态和该脉冲来到之前D的状态一样。表9-4所列触发器为下降沿触发。RHF310K-01V

集成D触器有TTL电路和CMOS电路。

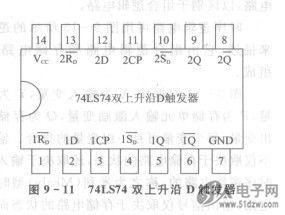

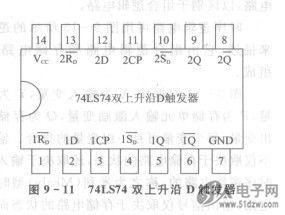

TTL电路如74LS74,引脚排列如图9- 11所示。741。S74是一块双上升沿D触发器,图中1,2打头的引脚分别为第一块和第二块D触发器的引脚。D端为输入端,Q端为输出端,Q端为反向输出端。SD为异步置“1”端(SD =O,置Q=l),RD为异步置“0”端(RD =0,置Q=O),平时SD,RD不用时应置为高电平。

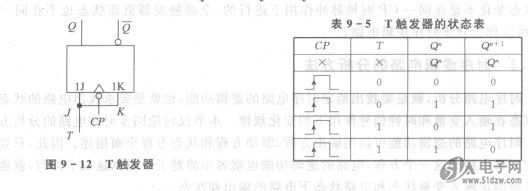

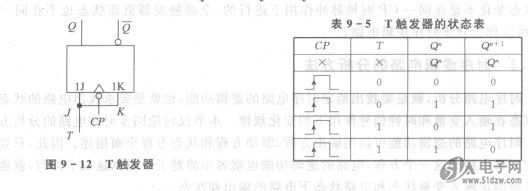

T触发器和T'触发器没有实际严品,一般由其他触发器来构成。如用JK触发器转换为T触发器如图9 -12所示,将JK触发器端连在一起,称为T端。当t=0时,时钟脉冲作用后触发器状态不变;当T=l时,触发器具有计数逻辑功能,其特性表如表9-5所列。

边沿D触发器逻辑电路符号如图9 -10所示。D触发器特性表如表9-4所列。D触发器具有在时钟脉冲上升沿(或下降沿)触发的特点,当时钟脉冲上升沿或下降沿时刻,输入端D的值传输到输出端,也就是说输出端Q的状态随着输入端D的值变化,即时钟脉冲来到之后Q的状态和该脉冲来到之前D的状态一样。表9-4所列触发器为下降沿触发。RHF310K-01V

集成D触器有TTL电路和CMOS电路。

TTL电路如74LS74,引脚排列如图9- 11所示。741。S74是一块双上升沿D触发器,图中1,2打头的引脚分别为第一块和第二块D触发器的引脚。D端为输入端,Q端为输出端,Q端为反向输出端。SD为异步置“1”端(SD =O,置Q=l),RD为异步置“0”端(RD =0,置Q=O),平时SD,RD不用时应置为高电平。

T触发器和T'触发器没有实际严品,一般由其他触发器来构成。如用JK触发器转换为T触发器如图9 -12所示,将JK触发器端连在一起,称为T端。当t=0时,时钟脉冲作用后触发器状态不变;当T=l时,触发器具有计数逻辑功能,其特性表如表9-5所列。

热门点击

热门点击

公网安备44030402000607

公网安备44030402000607