数字式调谐系统基础知识

发布时间:2011/12/10 10:10:23 访问次数:1655

1.数字式调谐系统种类

数字式调谐系统有下列两种。

2.频率合成器

3.锁相环路

锁相环路简称PLL(Phase Lock Loop,意为相位锁定环路)。

它利用鉴相器来锁定压控振荡器,T1042AB3以获得频率和相位都非常精确、稳定的特定频率。它有两个重要特性。

(1)窄带滤波特性。这一特性是不难理解的,由于在锁定状态下压控振荡器的输出频率和相位都被锁定,在这一频率附近的频率(大于或小于)都由于环路滤波器而大大受到抑制,对压控振荡器的干扰被减到很低程度,这种锁相环路就好像一个以压控振荡器工作频率为中心频率的带宽很小的带通滤波器。由此可见,锁相环路虽然不是一个LC选频电路,但具有极好的选择性和极高的品质因数,能获得高质量的特定频率。

(2)宽带跟踪特性。当输入信号频率和相位变化时,只要加宽环路频带,压控振荡器便能跟随输入信号频率和相位的变化。

4.锁相环式频率合成器

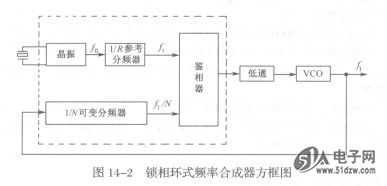

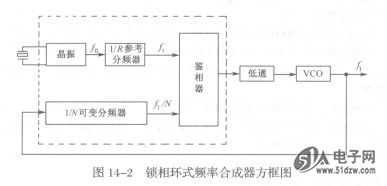

用图14-2所示方框图可以说明锁相环式频率合成器的电路组成和工作原理。

这一电路的工作原理:晶振是这一电路中的稳定、精确的频率源,它的频率fo质量非常高。fo经1/R参考分频器获得fo/R这一频率,记为fro同样,f的频率非常准确和稳定。fr加到鉴相器中,作为两个比较信号中的基准频率信号。

压控振荡器( VCO)产生的振荡频率石经1/N可变分频器分频后也加到鉴相器中,两输入信号经过频率和相位比较后,鉴相器输出的误差电压经低通滤波器后加到VCO上,使VCO工作频率变动,直到环路锁定。在环路锁定时VCO工作频率五是非常精确和稳定的,f1由下式决定: f1=Nfr

如改变分频比N,便可获得一系列频率间隔为f的稳定、精确的频率,如lOlfr、102fr、103fr、…。f1是本振频率,只要N取得恰当,便能使f1覆盖整个收音频段。

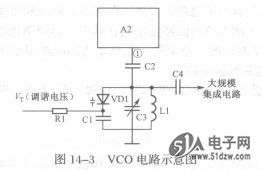

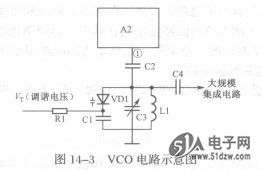

在实际电路中,低通滤波器和压控振荡器不设在大规模集成电路中。图中虚线框内的电路设在大规模集成电路内,这一集成电路有一个脚是鉴相器的直流电压(调谐电压)输出脚。VCO设在收音通道中,如图14-3所示。

从图14-3中可以看出,来自大规模集成电路的鉴相器输出电压(调谐电压VT),加到变容二极管VD1上,以改变Ll这一本振回路的频率。Ll和C3、Cl和VD1构成本振回路,为图14-2所示电路中的VCO。本振频率通过C2由①脚送入A2的内电路混频器中,同时本振信号(VCO输出信号f1)经C4送到大规模集成电路中的1/N可变分频器中(见图14-2所示电路)。

图14-3所示只表示了一个调谐回路,收音通道中的其他调谐回路电路结构和工作原理相同,并在同一波段时共用同一个调谐电压VT。

5.1/N可变分频器

见图14-2所示方框图,1/N可变分频器的作用有两个:一个是将VCO工作频率斤分频后降至fr大小,作为鉴相器的一个比较频率信号;二是可控制VCO工作频率,即改变分频比N时,可获得不同频率的f1,从而可控制合成器的输出频率石。

这里以调频波段( 87~108MHz)为例,讨论分频比N的变化范围。设频率间隔f为25kHz,则要求频率合成器输出的最低频率为87MHz+10.7MHz(中频)=97.7MHz,最小分频比为97.7MHz/25kHz=3908。要求频率合成器的最高输出频率为108MHz+10.7MHz=118.7MHz.最大分频比为118.7MHz/25kHz=4748。由此可知,在调频波段(87~108MHz)时,N的变化范围为3908~ 4748。

再讨论调幅中波段( 522~ 1605kHz)的Ⅳ变化范围,调幅中波段设f=500Hz,则要求频率合成器输出的最低频率为522kHz+465kHz(中频)=987kHz,最小分频比为987kHz/500Hz=1974。要求频率合成器在调幅中波段输出的最高频率为1605kHz+465kHz=2070kHz.最大分频比为2070kHz/500Hz= 4140。由此可知在中波段,Ⅳ的变化范围为1794~ 4140。

综合以上两种情况可以得出Ⅳ的变化范围为1794~ 4748。

在锁相环频率合成器中引入微处理器的程序控制,将1/N可变分频器变成可编程序分频器,由微处理器的程序控制实现Ⅳ的变化,从而获得所需要的工作频率石。

可编程序分频器由多级可变计数器和若干门电路构成,加上预置环节,通过预置环节等控制分频比N。

6.频率间隔fr

fr又称调谐步比,或称频率步跳间隔,见图14-2所示方框图,fr是通过fo/R分频后获得的,在不同收音波段取不同的R值,可获得不同的fr频率。

fr值取大些有利于提高调谐时搜索电台的速度,但fr太大会造成漏台现象,即fr大了在波段范围频率合成器输出的频率点少了,有的电台频率不在其中,便不能收到这一电台。如果减小fr,可尽量避免漏台现象,但调谐时搜索电台的速度又慢了。所以,fr的大小要取得恰当,多方兼顾。在一般情况下,中等性能的机器fr在调频段取25kHz,中波取500Hz,短波取5kHz。在高性能机器中,调频取5~ lOkHz.短波取lkHz。

7.脉冲吞除计数原理

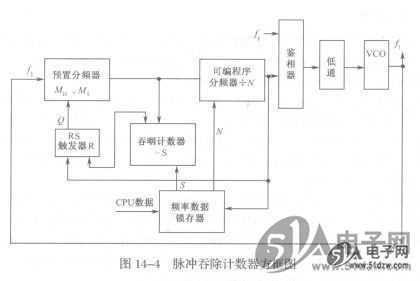

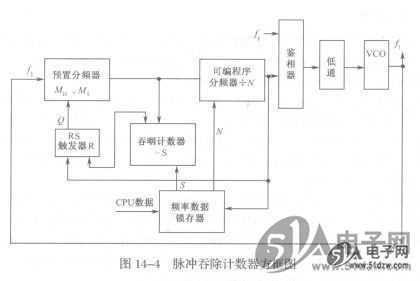

从前面的N计算可知,N最犬值为4748,在调频高端。N最小值为1974,在调幅中波的低端,这就要求可变分频器的分频比在1974~ 4748范围内变化,这对一般计数器来讲是非常复杂的,而且计数速度也难以提高。脉冲吞除计数器就是为解决这个问题才被引入锁相环频率合成器中的,这一计数器的电路结构和工作原理可用图14-4所示的方框图来说明。

这一电路的工作原理:预置分频器有两种分频比MH(高分频比)和坛(低分频比),设MH=17、ML=16。在计数开始时,数据锁存器将频率数据分别送入可编程序分频器÷N电路和吞咽计数器,VCO输出的频率f1经预置分频器以MH预分频后也分别送入吞咽计数器和可编程序分频器中,它们同时开始作减法计数。当吞咽计数器从预置的数S减法计数至0时,可编程序分频器也同样减去了S个数,此时吞咽计数器一方面输出一个换模信号给R-S触发器,使触发器置0,以控制预置分频器进入÷ML模式工作状态,另一方面也使吞咽计数器停止计数。接着剩下的百信号由预置分频器按÷ML分频后,再送到可编程序分频器中作减法计数,直到将N-S个数减完,可编程序分频器输出一个脉冲给频率数据锁存器,开始下一个周期的计数。

经过计算,这种分频率的总分频次数Nr由下式决定(MH=M+I): NT=MLN+S

式中,N、5都是由微处理器计算出来后送入频率数据锁存器,再分别送入吞咽计数器和可编程序分频器中。

这里以接收调频98MHz电台为例,根据前面介绍的计数方法得知总分频比为4348。微处理器将4348除以ML(16),得到的整数为N=271,这一数置给可编程序分频器,除16后的余数为S=12置给吞咽计数器。对不同的电台频率,N不同,其N和S也是不同的。

采用脉冲吞除计数器后可以简化电路结构、提高工作速度,故得到广泛应用。

8.常用DTS集成电路

一个完整的DTS系统通常由三块集成电路构成:

第一块是大规模集成电路,它含有锁相环频率合成器的主干电路和微处理器,其集成电路型号有TC9137P、 TC91-37AP、 TC9157AP和htPD1700系列(UPD1701C、 UPD1703C、UPD1704C、yPD1706G、UPD1707G、yPD1708G、ltPD1710G、 htPD1711CU、UPD1712CU、I.tPD1713AG、yPD1714G租yPD1715G).

第二块是预分频器集成电路,即图14-4所示图中的预置分频器。这一集成电路的型号有HPB553AC、TD6104P等。

第三块是频率显示驱动集成电路,它用来驱动数字显示器件,显示字母和数字,指示接收频段和频率。

1.数字式调谐系统种类

数字式调谐系统有下列两种。

2.频率合成器

3.锁相环路

锁相环路简称PLL(Phase Lock Loop,意为相位锁定环路)。

它利用鉴相器来锁定压控振荡器,T1042AB3以获得频率和相位都非常精确、稳定的特定频率。它有两个重要特性。

(1)窄带滤波特性。这一特性是不难理解的,由于在锁定状态下压控振荡器的输出频率和相位都被锁定,在这一频率附近的频率(大于或小于)都由于环路滤波器而大大受到抑制,对压控振荡器的干扰被减到很低程度,这种锁相环路就好像一个以压控振荡器工作频率为中心频率的带宽很小的带通滤波器。由此可见,锁相环路虽然不是一个LC选频电路,但具有极好的选择性和极高的品质因数,能获得高质量的特定频率。

(2)宽带跟踪特性。当输入信号频率和相位变化时,只要加宽环路频带,压控振荡器便能跟随输入信号频率和相位的变化。

4.锁相环式频率合成器

用图14-2所示方框图可以说明锁相环式频率合成器的电路组成和工作原理。

这一电路的工作原理:晶振是这一电路中的稳定、精确的频率源,它的频率fo质量非常高。fo经1/R参考分频器获得fo/R这一频率,记为fro同样,f的频率非常准确和稳定。fr加到鉴相器中,作为两个比较信号中的基准频率信号。

压控振荡器( VCO)产生的振荡频率石经1/N可变分频器分频后也加到鉴相器中,两输入信号经过频率和相位比较后,鉴相器输出的误差电压经低通滤波器后加到VCO上,使VCO工作频率变动,直到环路锁定。在环路锁定时VCO工作频率五是非常精确和稳定的,f1由下式决定: f1=Nfr

如改变分频比N,便可获得一系列频率间隔为f的稳定、精确的频率,如lOlfr、102fr、103fr、…。f1是本振频率,只要N取得恰当,便能使f1覆盖整个收音频段。

在实际电路中,低通滤波器和压控振荡器不设在大规模集成电路中。图中虚线框内的电路设在大规模集成电路内,这一集成电路有一个脚是鉴相器的直流电压(调谐电压)输出脚。VCO设在收音通道中,如图14-3所示。

从图14-3中可以看出,来自大规模集成电路的鉴相器输出电压(调谐电压VT),加到变容二极管VD1上,以改变Ll这一本振回路的频率。Ll和C3、Cl和VD1构成本振回路,为图14-2所示电路中的VCO。本振频率通过C2由①脚送入A2的内电路混频器中,同时本振信号(VCO输出信号f1)经C4送到大规模集成电路中的1/N可变分频器中(见图14-2所示电路)。

图14-3所示只表示了一个调谐回路,收音通道中的其他调谐回路电路结构和工作原理相同,并在同一波段时共用同一个调谐电压VT。

5.1/N可变分频器

见图14-2所示方框图,1/N可变分频器的作用有两个:一个是将VCO工作频率斤分频后降至fr大小,作为鉴相器的一个比较频率信号;二是可控制VCO工作频率,即改变分频比N时,可获得不同频率的f1,从而可控制合成器的输出频率石。

这里以调频波段( 87~108MHz)为例,讨论分频比N的变化范围。设频率间隔f为25kHz,则要求频率合成器输出的最低频率为87MHz+10.7MHz(中频)=97.7MHz,最小分频比为97.7MHz/25kHz=3908。要求频率合成器的最高输出频率为108MHz+10.7MHz=118.7MHz.最大分频比为118.7MHz/25kHz=4748。由此可知,在调频波段(87~108MHz)时,N的变化范围为3908~ 4748。

再讨论调幅中波段( 522~ 1605kHz)的Ⅳ变化范围,调幅中波段设f=500Hz,则要求频率合成器输出的最低频率为522kHz+465kHz(中频)=987kHz,最小分频比为987kHz/500Hz=1974。要求频率合成器在调幅中波段输出的最高频率为1605kHz+465kHz=2070kHz.最大分频比为2070kHz/500Hz= 4140。由此可知在中波段,Ⅳ的变化范围为1794~ 4140。

综合以上两种情况可以得出Ⅳ的变化范围为1794~ 4748。

在锁相环频率合成器中引入微处理器的程序控制,将1/N可变分频器变成可编程序分频器,由微处理器的程序控制实现Ⅳ的变化,从而获得所需要的工作频率石。

可编程序分频器由多级可变计数器和若干门电路构成,加上预置环节,通过预置环节等控制分频比N。

6.频率间隔fr

fr又称调谐步比,或称频率步跳间隔,见图14-2所示方框图,fr是通过fo/R分频后获得的,在不同收音波段取不同的R值,可获得不同的fr频率。

fr值取大些有利于提高调谐时搜索电台的速度,但fr太大会造成漏台现象,即fr大了在波段范围频率合成器输出的频率点少了,有的电台频率不在其中,便不能收到这一电台。如果减小fr,可尽量避免漏台现象,但调谐时搜索电台的速度又慢了。所以,fr的大小要取得恰当,多方兼顾。在一般情况下,中等性能的机器fr在调频段取25kHz,中波取500Hz,短波取5kHz。在高性能机器中,调频取5~ lOkHz.短波取lkHz。

7.脉冲吞除计数原理

从前面的N计算可知,N最犬值为4748,在调频高端。N最小值为1974,在调幅中波的低端,这就要求可变分频器的分频比在1974~ 4748范围内变化,这对一般计数器来讲是非常复杂的,而且计数速度也难以提高。脉冲吞除计数器就是为解决这个问题才被引入锁相环频率合成器中的,这一计数器的电路结构和工作原理可用图14-4所示的方框图来说明。

这一电路的工作原理:预置分频器有两种分频比MH(高分频比)和坛(低分频比),设MH=17、ML=16。在计数开始时,数据锁存器将频率数据分别送入可编程序分频器÷N电路和吞咽计数器,VCO输出的频率f1经预置分频器以MH预分频后也分别送入吞咽计数器和可编程序分频器中,它们同时开始作减法计数。当吞咽计数器从预置的数S减法计数至0时,可编程序分频器也同样减去了S个数,此时吞咽计数器一方面输出一个换模信号给R-S触发器,使触发器置0,以控制预置分频器进入÷ML模式工作状态,另一方面也使吞咽计数器停止计数。接着剩下的百信号由预置分频器按÷ML分频后,再送到可编程序分频器中作减法计数,直到将N-S个数减完,可编程序分频器输出一个脉冲给频率数据锁存器,开始下一个周期的计数。

经过计算,这种分频率的总分频次数Nr由下式决定(MH=M+I): NT=MLN+S

式中,N、5都是由微处理器计算出来后送入频率数据锁存器,再分别送入吞咽计数器和可编程序分频器中。

这里以接收调频98MHz电台为例,根据前面介绍的计数方法得知总分频比为4348。微处理器将4348除以ML(16),得到的整数为N=271,这一数置给可编程序分频器,除16后的余数为S=12置给吞咽计数器。对不同的电台频率,N不同,其N和S也是不同的。

采用脉冲吞除计数器后可以简化电路结构、提高工作速度,故得到广泛应用。

8.常用DTS集成电路

一个完整的DTS系统通常由三块集成电路构成:

第一块是大规模集成电路,它含有锁相环频率合成器的主干电路和微处理器,其集成电路型号有TC9137P、 TC91-37AP、 TC9157AP和htPD1700系列(UPD1701C、 UPD1703C、UPD1704C、yPD1706G、UPD1707G、yPD1708G、ltPD1710G、 htPD1711CU、UPD1712CU、I.tPD1713AG、yPD1714G租yPD1715G).

第二块是预分频器集成电路,即图14-4所示图中的预置分频器。这一集成电路的型号有HPB553AC、TD6104P等。

第三块是频率显示驱动集成电路,它用来驱动数字显示器件,显示字母和数字,指示接收频段和频率。

上一篇:基本知识

热门点击

热门点击

- 肖特基二极管外形特征和电路符号

- 四种限幅放大器

- 换气扇的安装方法应根据安装位置的具体条件决定

- 频率/电压转换电路

- TTL与非门构成的单稳态触发器

- 光电耦合器的作用

- 乙类互补对称功率放大器

- 晶体管的基本工作原理

- 全波整流器

- 液压机构工作原理

推荐技术资料

推荐技术资料

- 中国传媒大学传媒博物馆开

- 传媒博物馆开馆仪式隆童举行。教育都i国家广电总局等部门... [详细]

公网安备44030402000607

公网安备44030402000607