K8D1716UBC/K8D1716UTC是NOR闪速存储器吗?

发布时间:2011/7/12 10:36:27 访问次数:738

K8D1716UBC/K8D1716UTC 16Mbit (2M×8bit/lM×16bit)双Bank NOR闪速存储器电路的基本特性:

1) 单电压Vcc范围为2.7―3.6V(读/写操作电压);

2) 结构为1048576bit×16bit(字模式);

3) 快速读存取时间为70ns;

4) 编程/擦除操作时读;

5) 双Bank体系结构为Bankl/Bank2,8Mbit/8Mbit;

6) 安全码块为额外的64KB块;

7) 功率消耗(典型值5MHz时),即①读电流为14mA,

②编程/擦除电流为15mA,

③编程时读或擦除时读电流为25mA,

④待机模式/自动睡眠模式为5μA;

8) WP/Vcc输入引脚,即①在VIL时允许2个最外层的启动区特殊保护,与块保护状态无关,

②在VIH时删除2个最外层的启动区特殊保护,2个块恢复正常块保护状态,

③在VHH时编程时间为9μs/字;

9)擦除暂停/恢复;

10)解锁旁路编程;

11)硬件RESET刳脚;

12)控制寄存器操作;

13)块组保护/非保护;

14)支持通用的闪速存储器接口;

15)工业级温度范围为- 40~ 85℃;

16)100000次编程/擦除周期;

17)10年数据保留;

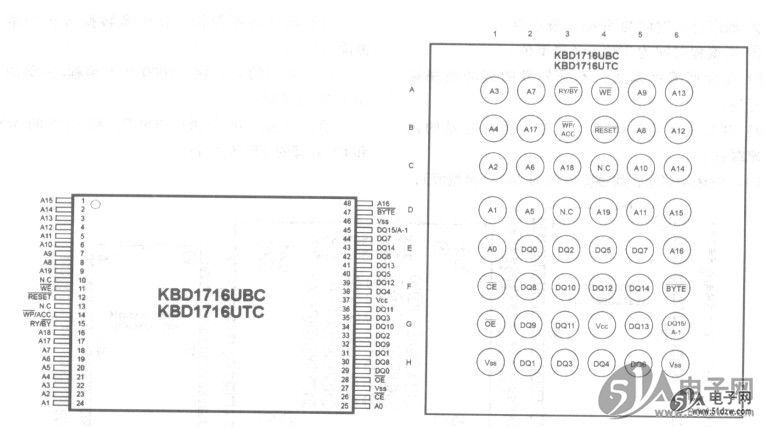

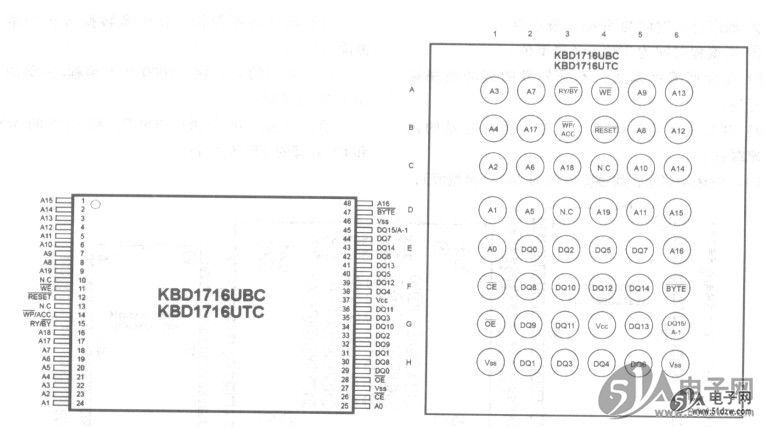

18)封装,48引脚TSOP和48引脚FBGA封装。

K8D1716UBC/K8D1716UTC 16Mbit (2M×8bit/lM×16bit)双Bank NOR闪速存储器电路的基本特性:

1) 单电压Vcc范围为2.7―3.6V(读/写操作电压);

2) 结构为1048576bit×16bit(字模式);

3) 快速读存取时间为70ns;

4) 编程/擦除操作时读;

5) 双Bank体系结构为Bankl/Bank2,8Mbit/8Mbit;

6) 安全码块为额外的64KB块;

7) 功率消耗(典型值5MHz时),即①读电流为14mA,

②编程/擦除电流为15mA,

③编程时读或擦除时读电流为25mA,

④待机模式/自动睡眠模式为5μA;

8) WP/Vcc输入引脚,即①在VIL时允许2个最外层的启动区特殊保护,与块保护状态无关,

②在VIH时删除2个最外层的启动区特殊保护,2个块恢复正常块保护状态,

③在VHH时编程时间为9μs/字;

9)擦除暂停/恢复;

10)解锁旁路编程;

11)硬件RESET刳脚;

12)控制寄存器操作;

13)块组保护/非保护;

14)支持通用的闪速存储器接口;

15)工业级温度范围为- 40~ 85℃;

16)100000次编程/擦除周期;

17)10年数据保留;

18)封装,48引脚TSOP和48引脚FBGA封装。

公网安备44030402000607

公网安备44030402000607