1000小时HV-H3TRB测试显示对高压及潮湿环境卓越适应能力

发布时间:2024/3/5 8:23:24 访问次数:519

设计规则检查 (DRC) 技术用于芯片设计,可确保以较高的良率制造出所需器件。

在先进的半导体技术节点,DRC规则的数量增加和复杂性提升,导致传统的2D DRC无法识别所有热点和故障。2D DRC无法模拟或预测3D规则违规,因此通常在开发晚期才能识别到3D故障。仅靠硅晶圆厂数据和测试宏来识别开发晚期的故障既耗时又昂贵。

SEMulator3D®虚拟制造平台可用于进行半导体器件的3D建模和基于规则的量测,并用比硅晶圆实验更快、更经济的方式识别热点(DRC违规)和潜在故障。

取电协议芯片与充电头(Source) 进行协商,Type-C通过控制信号输出协商电压,然后充电管理多串锂电池或其它类型电池充电。

设计规则通常根据所使用设备和工艺技术的限制和变异性制定。DRC可确保设计符合制造要求,且不会导致芯片故障或DRC违规。常见的DRC规则包括最小宽度和间隔要求、偏差检查以及其他规格,以避免在制造过程中出现短路、断路、材料过量或其他器件故障。

测试电压的大幅提升对于IGBT无疑是更严峻的考验,而IGBT7通过优化设计,通过了1000小时的HV-H3TRB测试,显示出对高压及潮湿环境的卓越适应能力。

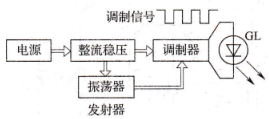

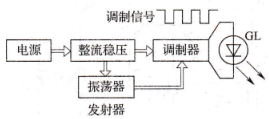

此外还会产生少量的电源调制噪声,如测量的电源调制比(PSMR)。该PSMR是对调制到RF发射载波上的缺陷(纹波和噪声)的测量。可以使用非隔离的RF负载点调节器(PMIC中的RF PoL)来减少或消除这种噪声。

实施RF PoL/PMIC可为RFFE应用带来最佳运行所需的高精度电压轨、快速动态响应负载,和低噪声。

设计规则检查 (DRC) 技术用于芯片设计,可确保以较高的良率制造出所需器件。

在先进的半导体技术节点,DRC规则的数量增加和复杂性提升,导致传统的2D DRC无法识别所有热点和故障。2D DRC无法模拟或预测3D规则违规,因此通常在开发晚期才能识别到3D故障。仅靠硅晶圆厂数据和测试宏来识别开发晚期的故障既耗时又昂贵。

SEMulator3D®虚拟制造平台可用于进行半导体器件的3D建模和基于规则的量测,并用比硅晶圆实验更快、更经济的方式识别热点(DRC违规)和潜在故障。

取电协议芯片与充电头(Source) 进行协商,Type-C通过控制信号输出协商电压,然后充电管理多串锂电池或其它类型电池充电。

设计规则通常根据所使用设备和工艺技术的限制和变异性制定。DRC可确保设计符合制造要求,且不会导致芯片故障或DRC违规。常见的DRC规则包括最小宽度和间隔要求、偏差检查以及其他规格,以避免在制造过程中出现短路、断路、材料过量或其他器件故障。

测试电压的大幅提升对于IGBT无疑是更严峻的考验,而IGBT7通过优化设计,通过了1000小时的HV-H3TRB测试,显示出对高压及潮湿环境的卓越适应能力。

此外还会产生少量的电源调制噪声,如测量的电源调制比(PSMR)。该PSMR是对调制到RF发射载波上的缺陷(纹波和噪声)的测量。可以使用非隔离的RF负载点调节器(PMIC中的RF PoL)来减少或消除这种噪声。

实施RF PoL/PMIC可为RFFE应用带来最佳运行所需的高精度电压轨、快速动态响应负载,和低噪声。

热门点击

热门点击

公网安备44030402000607

公网安备44030402000607