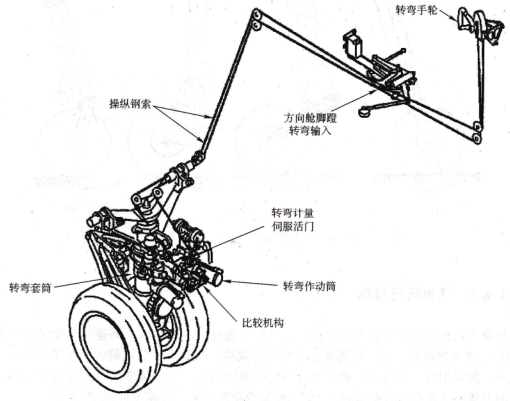

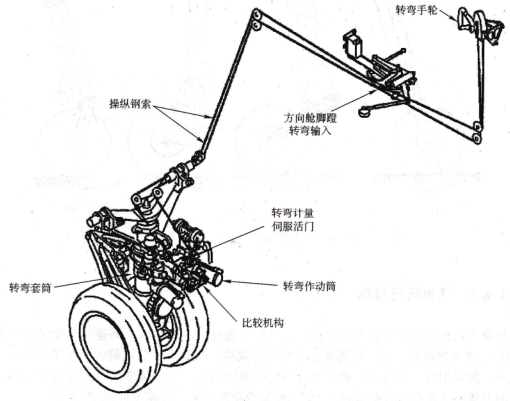

中央操纵机构附近有极限偏转角度止动器防止驾驶员用力过猛

发布时间:2023/12/16 19:30:22 访问次数:103

Ncore 3的独特之处是它可以让同一块芯片上采用AMBA CHI以及ACE等不同一致性协议处理器群组和加速器作为完全一致性(Fully Coherent)对等节点运行,因而设计团队可以灵活选择CPU和硬件加速器IP。

ArterisIP CHI接口包括支持高阶的一致性协议,例如高性能SoC使用的Atomic和Cache Stashing。

Ncore Cache Coherent Interconnect for Accelerators (CCIX) controller 能透过Synopsys® DesignWare® 上PCI Express和CCIX的控制器和PHY IP,在多个芯片间轻易扩展一致性系统。

为了实现针对汽车市场的高级系统,Ncore 3产品线还包括可选配的Ncore Resilience Package。

为防止驾驶员无意识动杆及减轻驾驶员的疲劳,操纵系统的启动力应在合适的范围内。

在中央操纵机构附近应有极限偏转角度止动器,以防止驾驶员用力过猛,操纵过量而使系统中某些部件或机体结构遭到损坏;

飞机停在地面上时,为防止舵面被大风吹坏,所有舵面应用“锁”来固定。舵面锁紧系统应在飞机内部,不应采用外部锁紧装置,内锁紧装置应直接与舵面连接。为防止在起飞状态下,舵面仍处于锁定状态,要求必须在所有舵面都开锁后,油门才能打开。

然而更为“理想”,也意味着需要付出更多的代价。AMOLED显示屏的“伤眼说”更多来源于外界对于当前AMOLED制造商普遍采用PWM低频调光的不满。这里简单解释下PWM低频调光技术。

所有的显示器都具备亮度调节功能,但由于材质的区别,调光的技术各不相同,当前智能手机上最为主流的莫过于DC调光和PWM调光。

Ncore 3的独特之处是它可以让同一块芯片上采用AMBA CHI以及ACE等不同一致性协议处理器群组和加速器作为完全一致性(Fully Coherent)对等节点运行,因而设计团队可以灵活选择CPU和硬件加速器IP。

ArterisIP CHI接口包括支持高阶的一致性协议,例如高性能SoC使用的Atomic和Cache Stashing。

Ncore Cache Coherent Interconnect for Accelerators (CCIX) controller 能透过Synopsys® DesignWare® 上PCI Express和CCIX的控制器和PHY IP,在多个芯片间轻易扩展一致性系统。

为了实现针对汽车市场的高级系统,Ncore 3产品线还包括可选配的Ncore Resilience Package。

为防止驾驶员无意识动杆及减轻驾驶员的疲劳,操纵系统的启动力应在合适的范围内。

在中央操纵机构附近应有极限偏转角度止动器,以防止驾驶员用力过猛,操纵过量而使系统中某些部件或机体结构遭到损坏;

飞机停在地面上时,为防止舵面被大风吹坏,所有舵面应用“锁”来固定。舵面锁紧系统应在飞机内部,不应采用外部锁紧装置,内锁紧装置应直接与舵面连接。为防止在起飞状态下,舵面仍处于锁定状态,要求必须在所有舵面都开锁后,油门才能打开。

然而更为“理想”,也意味着需要付出更多的代价。AMOLED显示屏的“伤眼说”更多来源于外界对于当前AMOLED制造商普遍采用PWM低频调光的不满。这里简单解释下PWM低频调光技术。

所有的显示器都具备亮度调节功能,但由于材质的区别,调光的技术各不相同,当前智能手机上最为主流的莫过于DC调光和PWM调光。

公网安备44030402000607

公网安备44030402000607