数据I/O总线上相对于DQS触发的时间间隔被称为tAC

发布时间:2023/9/15 22:58:39 访问次数:105

DDR SDRAM对时钟的精确性有着很高的要求,而DDR SDRAM有两个时钟,一个是外部的总线时钟,一个是内部的工作时钟,在理论上DDR SDRAM这两个时钟应该是同步的,但由于种种原因,如温度、电压波动而产生延迟使两者很难同步,更何况时钟频率本身也有不稳定的情况(SDRAM也内部时钟,不过因为它的工作/传输频率较低,所以内外同步问题并不突出)。

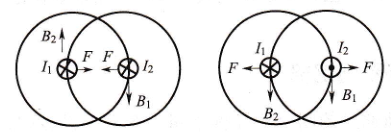

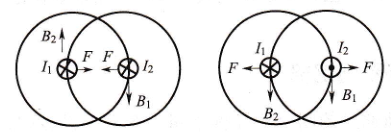

MAX9626–MAX9628的输出共模电压通过一个输入引脚(VOCM)设置,无需使用耦合变压器或交流耦合电容。这种方式能够避免外部元件非理想特性的影响,因而可节省电路板空间、提高性能。

为满足轻薄型产品的需求,BGA(Ball grid arrya)封装的64pin及113pin产品,尺寸分别为5mmx5mm、6mmx6mm,进一步减小封装面积,有助于实现整机的小型化。

随着产品线的扩充,“V850ES/Jx3”系列产品从闪存16KB到1MB,外部引脚数量从40pin到144pin共计117款产品。

全新推广的产品非常适合电池驱动的消费电子产品及电脑周边产品、健康器械、工业设备,有助于提高整机竞争力。日后,将继续扩充产品线并积极推广全线产品。

在读取时,DQS与数据信号同时生成(也是在CK与CK#的交叉点)。而DDR内存中的CL也就是从CAS发出到DQS生成的间隔,数据真正出现在数据I/O总线上相对于DQS触发的时间间隔被称为tAC。注意,这与SDRAM中的tAC的不同。

实际上,DQS生成时,芯片内部的预取已经完毕了,tAC是指上文结构图中灰色部分的数据输出时间,由于预取的原因,实际的数据传出可能会提前于DQS发生(数据提前于DQS传出)。

使用了带PLL芯科IC为家用高性能微型音频设备。由于使用了高密度封装技术,相对传统的MITSUMI器件其面积减小40%。

深圳市慈安科技有限公司http://cakj.51dzw.com

DDR SDRAM对时钟的精确性有着很高的要求,而DDR SDRAM有两个时钟,一个是外部的总线时钟,一个是内部的工作时钟,在理论上DDR SDRAM这两个时钟应该是同步的,但由于种种原因,如温度、电压波动而产生延迟使两者很难同步,更何况时钟频率本身也有不稳定的情况(SDRAM也内部时钟,不过因为它的工作/传输频率较低,所以内外同步问题并不突出)。

MAX9626–MAX9628的输出共模电压通过一个输入引脚(VOCM)设置,无需使用耦合变压器或交流耦合电容。这种方式能够避免外部元件非理想特性的影响,因而可节省电路板空间、提高性能。

为满足轻薄型产品的需求,BGA(Ball grid arrya)封装的64pin及113pin产品,尺寸分别为5mmx5mm、6mmx6mm,进一步减小封装面积,有助于实现整机的小型化。

随着产品线的扩充,“V850ES/Jx3”系列产品从闪存16KB到1MB,外部引脚数量从40pin到144pin共计117款产品。

全新推广的产品非常适合电池驱动的消费电子产品及电脑周边产品、健康器械、工业设备,有助于提高整机竞争力。日后,将继续扩充产品线并积极推广全线产品。

在读取时,DQS与数据信号同时生成(也是在CK与CK#的交叉点)。而DDR内存中的CL也就是从CAS发出到DQS生成的间隔,数据真正出现在数据I/O总线上相对于DQS触发的时间间隔被称为tAC。注意,这与SDRAM中的tAC的不同。

实际上,DQS生成时,芯片内部的预取已经完毕了,tAC是指上文结构图中灰色部分的数据输出时间,由于预取的原因,实际的数据传出可能会提前于DQS发生(数据提前于DQS传出)。

使用了带PLL芯科IC为家用高性能微型音频设备。由于使用了高密度封装技术,相对传统的MITSUMI器件其面积减小40%。

深圳市慈安科技有限公司http://cakj.51dzw.com

公网安备44030402000607

公网安备44030402000607