Virage可重置嵌入式存储器能优化整个结构中读写端口大小

发布时间:2022/12/29 13:32:45 访问次数:176

共享存储器能使系统级芯片(SoC)设计增加数据95%,而不增加芯片面积。

基于SRAM的客户面积,速度和功率(ASAP)高速多端口寄存器文件嵌入式存储器,Virage 一种用在高速SoC设计的共享存储器系统。这种系统的应用推动DSP,NPU或图形芯片的复合应用,有高的吞吐量而不用牺牲硅芯片面积。

Virage的可重置嵌入式存储器能优化成整个结构中的读写端口那样的大小。存储器还有用户控制的选择功能,它允许在同一时钟周期,用时钟的两个边缘在同样的地址进行读和写操作,从而数据速率双倍(DDR)。

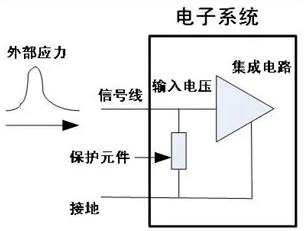

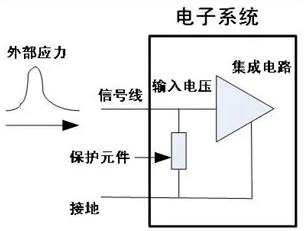

CM3014还有可选择的旁路引脚,当连接时,能改善电源的波纹抑制和具有35 μVrms的低噪音,能从嘈杂的输入中得到干净的输出电压,以保证专用集成电路(ASIC)的正常工作。

POSIC10G是一种真正的单芯片10GbE方案,它集成了10GbE媒体访问控制器(MAC)、SONET/SDH成帧器、物理编码子层(PCS)和WAN接口子层(WIS)。该器件可有效处理10GbE数据包,支持大容量帧和地址过滤。

POSIC10G还支持10 Gbps线卡上网络处理器业界标准SPI4.2。该芯片带有两个片上SONET/SDH成帧器模块,可为SONET的自动保护服务(APS)提供高级支持。

APS交换/恢复既可人工完成,也可自动实现,因此为客户网络提供了灵活的冗余选项。

因为不损害到数据的完整性,因此也能从任何区域同时读取数据。因为多端口寄存器文件嵌入式存储器在SoC设计时是可重新配置的,设计者能进行"如果将会怎样"的分析和调整芯片的系统结构以满足所需的面积,速度和功率(ASAP)。

上海德懿电子科技有限公司 www.deyie.com

共享存储器能使系统级芯片(SoC)设计增加数据95%,而不增加芯片面积。

基于SRAM的客户面积,速度和功率(ASAP)高速多端口寄存器文件嵌入式存储器,Virage 一种用在高速SoC设计的共享存储器系统。这种系统的应用推动DSP,NPU或图形芯片的复合应用,有高的吞吐量而不用牺牲硅芯片面积。

Virage的可重置嵌入式存储器能优化成整个结构中的读写端口那样的大小。存储器还有用户控制的选择功能,它允许在同一时钟周期,用时钟的两个边缘在同样的地址进行读和写操作,从而数据速率双倍(DDR)。

CM3014还有可选择的旁路引脚,当连接时,能改善电源的波纹抑制和具有35 μVrms的低噪音,能从嘈杂的输入中得到干净的输出电压,以保证专用集成电路(ASIC)的正常工作。

POSIC10G是一种真正的单芯片10GbE方案,它集成了10GbE媒体访问控制器(MAC)、SONET/SDH成帧器、物理编码子层(PCS)和WAN接口子层(WIS)。该器件可有效处理10GbE数据包,支持大容量帧和地址过滤。

POSIC10G还支持10 Gbps线卡上网络处理器业界标准SPI4.2。该芯片带有两个片上SONET/SDH成帧器模块,可为SONET的自动保护服务(APS)提供高级支持。

APS交换/恢复既可人工完成,也可自动实现,因此为客户网络提供了灵活的冗余选项。

因为不损害到数据的完整性,因此也能从任何区域同时读取数据。因为多端口寄存器文件嵌入式存储器在SoC设计时是可重新配置的,设计者能进行"如果将会怎样"的分析和调整芯片的系统结构以满足所需的面积,速度和功率(ASAP)。

上海德懿电子科技有限公司 www.deyie.com

公网安备44030402000607

公网安备44030402000607