֡���ȼ���SPI�����ⲿ����ӵ��辭��ס-14V��6V��ѹ

����ʱ��:2022/1/19 12:35:17 ���ʴ���:1044

65�����߿���Quad Data Rate (QDR) ��Double Data Rate (DDR) SRAM������Ʒ��

���Ƴ���72-Mbit QDRII��QDRII+��DDRII��DDRII+�洢��������������˹������������� UMC �����Ĺ��ռ�����

QDRII+��DDRII+��������Ƭ���ս������ (ODT)���������ⲿ����ӵ����Ҫ�����������źŵ������ԣ�����ϵͳ�ɱ�����Լ���Ͽռ䡣65���ײ�Ʒ���õ������· (PLL) �����ӳ���� (DLL) ���������ʹ������Ч������չ35%�������ͻ����̿���ʱ�䡢��Լ�����ɱ���

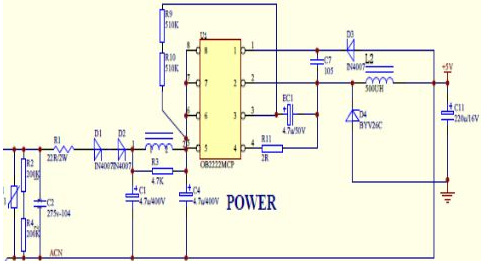

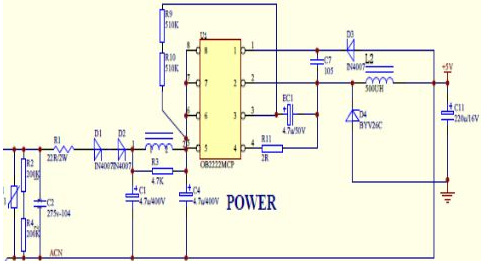

32λʧ��֡SPI�ӽӿ�ʵ��L9908��uC��ͨ��,���ʸߴ�10MHz.SPIͨ����5λCRC,1λ֡������,֡���ȼ���SPI���õ��Ӵ����Ź��Ȱ�ȫ��֤.��������AEC-Q100����,��ȫ�� ISO26262����, ASIL-Dϵͳ����.��VDD���ŵ�5V��ѹ����3.3V�ڲ���Դ.

�����ڵ�12Vϵͳ,˫(24Vϵͳ)��48V���Ӧ��,VDH�����Դ��Χ��4.5V��75V.SPI�ɵ�������ϵ�������ʧ��,���������У,�����������ܾ���ס-14V��6V��ѹ.

���ڹ���ģ�龧Բ���ӳ��ڹ�Ӧ��ȫ���ǣ����ǵϰ뵼���ȡ���ƾ�ԲΪ�����������Ϊ�����������,2018-2020�ꡢ2021��1-6���侧Բ���������ʷֱ�Ϊ78.61%��49.54%��32.33%��64.05%��

��������������ʵ��BrainChip������������ṩ�ij���������������ѧϰ���ص㡣����ЩоƬ���������ܶ������������һ���˹����ܳ�Ϊ��ʵ�ķ�ʽ��BrainChip������ϵͳ�����̺Ϳ�����Ա�ṩ������PCIe��Ʋ����ļ��Ͳ����嵥 (BOM)��ʹ�����ܹ������Լ��ĵ�·�岢����AKD1000оƬ��Ϊ����Ƕ��ʽ��������Э������������

(�ز���Դ��ת��������,�����Ȩ����ϵɾ��,�ر��л��

65�����߿���Quad Data Rate (QDR) ��Double Data Rate (DDR) SRAM������Ʒ��

���Ƴ���72-Mbit QDRII��QDRII+��DDRII��DDRII+�洢��������������˹������������� UMC �����Ĺ��ռ�����

QDRII+��DDRII+��������Ƭ���ս������ (ODT)���������ⲿ����ӵ����Ҫ�����������źŵ������ԣ�����ϵͳ�ɱ�����Լ���Ͽռ䡣65���ײ�Ʒ���õ������· (PLL) �����ӳ���� (DLL) ���������ʹ������Ч������չ35%�������ͻ����̿���ʱ�䡢��Լ�����ɱ���

32λʧ��֡SPI�ӽӿ�ʵ��L9908��uC��ͨ��,���ʸߴ�10MHz.SPIͨ����5λCRC,1λ֡������,֡���ȼ���SPI���õ��Ӵ����Ź��Ȱ�ȫ��֤.��������AEC-Q100����,��ȫ�� ISO26262����, ASIL-Dϵͳ����.��VDD���ŵ�5V��ѹ����3.3V�ڲ���Դ.

�����ڵ�12Vϵͳ,˫(24Vϵͳ)��48V���Ӧ��,VDH�����Դ��Χ��4.5V��75V.SPI�ɵ�������ϵ�������ʧ��,���������У,�����������ܾ���ס-14V��6V��ѹ.

���ڹ���ģ�龧Բ���ӳ��ڹ�Ӧ��ȫ���ǣ����ǵϰ뵼���ȡ���ƾ�ԲΪ�����������Ϊ�����������,2018-2020�ꡢ2021��1-6���侧Բ���������ʷֱ�Ϊ78.61%��49.54%��32.33%��64.05%��

��������������ʵ��BrainChip������������ṩ�ij���������������ѧϰ���ص㡣����ЩоƬ���������ܶ������������һ���˹����ܳ�Ϊ��ʵ�ķ�ʽ��BrainChip������ϵͳ�����̺Ϳ�����Ա�ṩ������PCIe��Ʋ����ļ��Ͳ����嵥 (BOM)��ʹ�����ܹ������Լ��ĵ�·�岢����AKD1000оƬ��Ϊ����Ƕ��ʽ��������Э������������

(�ز���Դ��ת��������,�����Ȩ����ϵɾ��,�ر��л��

�������

�������

- 5.7��12.1Ӣ��X2���߶���Ӧ�û��뽻��

- AX2557�ṩ48����fcLGA��װ���ƽ�

- 12~30AWG�߾����ṩ�Ӻϱ�����������

- ��ҵ�˶����Ƶ�Ԫ�е��ŷ�����ǺͶ�̬�������

- ������оƬ��ʡ��·�����40%�湦�ʹܵ�����

- ��̬������1A����LEͨ�������������ǿ

- �����ѹ��8VDC��450VDC��Χ������Ч

- �ᱡ�ͼ�����ʽģ�����о�ıպϴ�·ͨ�ž�

- RapidIOͨ��Э�����CORBA��Ʒ�е�

- ����դ��������TPS23753A�ܵ��豸 (

�Ƽ���������

�Ƽ���������

- ��Դ��ѹ������

- ���Ľ����S=34mm��60mm�� &nbs... [��ϸ]

- PWM���빦������������ԭ��

- ����ʽ DC/DC �任����ģ

- �������4 ����Ч��ѹ DC/

- ���ָ��빦��ȫ���� DC/DC

- ���ɵ�������������ģ��ת���� (ADC)Ӧ��

- 128 ͨ��20 λ��������ת����Ӧ��̽��

- ��ý��Э������SM501��Ƕ��ʽϵͳ�е�Ӧ��

- ����IEEE802.11b��EPA�¶ȱ�����

- QUICCEngine�������ƶ�IP�������

- SoC���������IJ�ҵ����

- MPC8xxϵ�д�������Ƕ��ʽϵͳ��Դ���

- dsPIC�����ڽ�����Ƶ�����е�Ӧ���о�

��������44030402000607

��������44030402000607