晶体管有源区(AA)尺寸改进的Gysel功分网络具有幅度均衡功能

发布时间:2021/8/30 22:28:28 访问次数:200

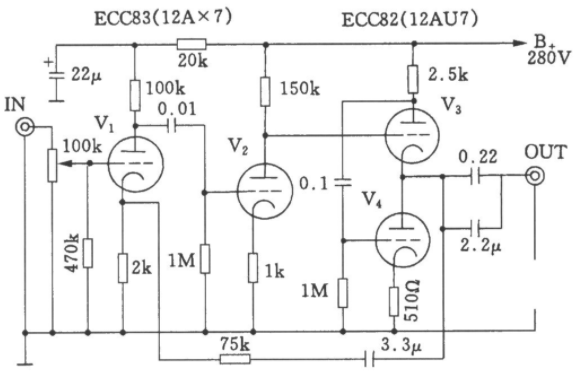

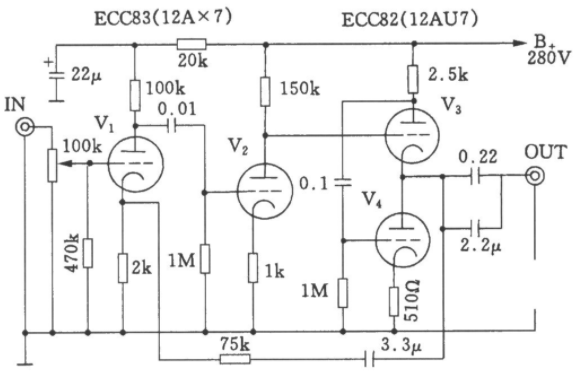

S21和S31幅频特性外,各端口驻波特性对最终产品的工作稳定性尤为重要。

典型的1:2 Gysel各端口的反射系数优于-20 dB,S21和S31一致性很好,插损在-3.11 dB和-3.17 dB之间,起伏非常小甚至可以忽略不计,这是Gysel的常规用法。

改进的Gysel功分网络具有幅度均衡功能,换言之,可以实现功分网络和均衡网络的一体化设计。

为了达到设计目的,Z1,Z2和Z3不取传统意义上的阻抗值,把其长度L和宽度W均设为可调节的变量,并且采用分频段设置优化目标的方法来满足特殊的幅度均衡要求。

制造商: Infineon

产品种类: 门驱动器

RoHS: 详细信息

产品: Half-Bridge Drivers

类型: Half-Bridge

安装风格: Through Hole

封装 / 箱体: DIP-8

激励器数量: 2 Driver

输出端数量: 2 Output

输出电流: 230 mA

电源电压-最小: 12.6 V

电源电压-最大: 15.4 V

配置: High Side, Low Side

上升时间: 150 ns

下降时间: 75 ns

最小工作温度: - 25 C

最大工作温度: + 125 C

封装: Tube

技术: Si

商标: Infineon / IR

工作电源电流: 10 mA

工作电源电压: 14 V

Pd-功率耗散: 1 W

产品类型: Gate Drivers

工厂包装数量: 3000

子类别: PMIC - Power Management ICs

单位重量: 2.268 g

随着晶体管尺寸缩小接近物理极限,制造变量和微负载效应正逐渐成为限制DRAM性能(和良率)的主要因素。

而对于先进的DRAM,晶体管的有源区 (AA) 尺寸和形状则是影响良率和性能的重要因素。

在DRAM结构中,电容存储单元的充放电过程直接受晶体管所控制。随着晶体管尺寸缩小接近物理极限,制造变量和微负载效应正逐渐成为限制DRAM性能(和良率)的主要因素。

而对于先进的DRAM,晶体管的有源区 (AA) 尺寸和形状则是影响良率和性能的重要因素。

(素材来源:eccn和ttic.如涉版权请联系删除。特别感谢)

S21和S31幅频特性外,各端口驻波特性对最终产品的工作稳定性尤为重要。

典型的1:2 Gysel各端口的反射系数优于-20 dB,S21和S31一致性很好,插损在-3.11 dB和-3.17 dB之间,起伏非常小甚至可以忽略不计,这是Gysel的常规用法。

改进的Gysel功分网络具有幅度均衡功能,换言之,可以实现功分网络和均衡网络的一体化设计。

为了达到设计目的,Z1,Z2和Z3不取传统意义上的阻抗值,把其长度L和宽度W均设为可调节的变量,并且采用分频段设置优化目标的方法来满足特殊的幅度均衡要求。

制造商: Infineon

产品种类: 门驱动器

RoHS: 详细信息

产品: Half-Bridge Drivers

类型: Half-Bridge

安装风格: Through Hole

封装 / 箱体: DIP-8

激励器数量: 2 Driver

输出端数量: 2 Output

输出电流: 230 mA

电源电压-最小: 12.6 V

电源电压-最大: 15.4 V

配置: High Side, Low Side

上升时间: 150 ns

下降时间: 75 ns

最小工作温度: - 25 C

最大工作温度: + 125 C

封装: Tube

技术: Si

商标: Infineon / IR

工作电源电流: 10 mA

工作电源电压: 14 V

Pd-功率耗散: 1 W

产品类型: Gate Drivers

工厂包装数量: 3000

子类别: PMIC - Power Management ICs

单位重量: 2.268 g

随着晶体管尺寸缩小接近物理极限,制造变量和微负载效应正逐渐成为限制DRAM性能(和良率)的主要因素。

而对于先进的DRAM,晶体管的有源区 (AA) 尺寸和形状则是影响良率和性能的重要因素。

在DRAM结构中,电容存储单元的充放电过程直接受晶体管所控制。随着晶体管尺寸缩小接近物理极限,制造变量和微负载效应正逐渐成为限制DRAM性能(和良率)的主要因素。

而对于先进的DRAM,晶体管的有源区 (AA) 尺寸和形状则是影响良率和性能的重要因素。

(素材来源:eccn和ttic.如涉版权请联系删除。特别感谢)

公网安备44030402000607

公网安备44030402000607