光耦合器的栅极驱动能力满足了CREE的98%的效率要求

发布时间:2021/8/28 13:32:44 访问次数:1424

Avago Technologies已与SiC市场领先者CREE Inc紧密合作,以确定适合SiC MOSFET操作的合适的栅极驱动光电耦合器。

利用Avago栅极驱动光电耦合器和CREE C2M0080120D SiC MOSFET实现高效率。

使用100 kHz的8A SEPIC DC-DC转换器评估了带有CREE C2M SiC MOSFET的栅极驱动光电耦合器ACPL-W346和ACPL-339J。

这两个光耦合器的栅极驱动能力满足了CREE的98%的效率要求。

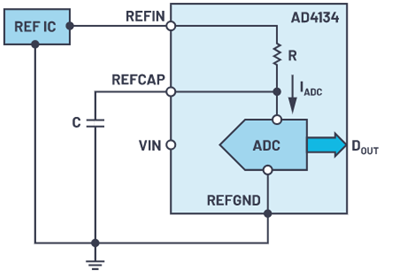

DAC更新速率提高到60 MSPS,并在各原始数据采样点之间插入“0”。

并行数据流为60 MSPS,但我们必须确定零值数据点的值,这通过将添加0的60 MSPS数据流经由数字插值滤波器处理来实现,由滤波器计算额外的数据点。

2× 过采样频率下的数字滤波器响应曲――模拟抗混叠滤波器过渡区现在是10 MHz到50 MHz(第一镜像出现在2fc - fo = 60 - 10 = 50 MHz)。

该过渡区稍大于2个倍频程,说明5或6极点滤波器即足够。

(素材来源:eccn和ttic.如涉版权请联系删除。特别感谢)

Avago Technologies已与SiC市场领先者CREE Inc紧密合作,以确定适合SiC MOSFET操作的合适的栅极驱动光电耦合器。

利用Avago栅极驱动光电耦合器和CREE C2M0080120D SiC MOSFET实现高效率。

使用100 kHz的8A SEPIC DC-DC转换器评估了带有CREE C2M SiC MOSFET的栅极驱动光电耦合器ACPL-W346和ACPL-339J。

这两个光耦合器的栅极驱动能力满足了CREE的98%的效率要求。

DAC更新速率提高到60 MSPS,并在各原始数据采样点之间插入“0”。

并行数据流为60 MSPS,但我们必须确定零值数据点的值,这通过将添加0的60 MSPS数据流经由数字插值滤波器处理来实现,由滤波器计算额外的数据点。

2× 过采样频率下的数字滤波器响应曲――模拟抗混叠滤波器过渡区现在是10 MHz到50 MHz(第一镜像出现在2fc - fo = 60 - 10 = 50 MHz)。

该过渡区稍大于2个倍频程,说明5或6极点滤波器即足够。

(素材来源:eccn和ttic.如涉版权请联系删除。特别感谢)

公网安备44030402000607

公网安备44030402000607