CMOS数字输出驱动器低压差分信号LVDS

发布时间:2020/11/14 12:07:55 访问次数:1092

模数转换器(ADC)可以选择,数字数据输出类型是选择过程中需要考虑的一项重要参数。目前,高速转换器三种最常用的数字输出是互补金属氧化物半导体(CMOS)、低压差分信号(LVDS)和电流模式逻辑(CML)。ADC中每种数字输出类型都各有优劣,设计人员应根据特定应用仔细考虑。

这些因素取决于ADC的采样速率和分辨率、输出数据速率、系统设计的电源要求,以及其他因素。每种输出类型的电气规格,及其适合特定应用的具体特点。我们将从物理实现、效率以及最适合每种类型的应用这些方面来对比这些不同类型的输出。

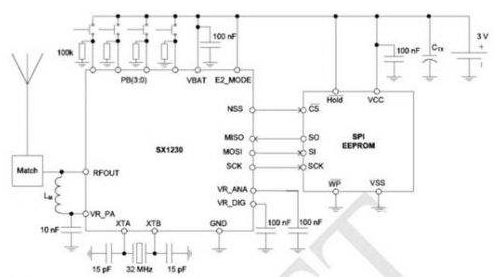

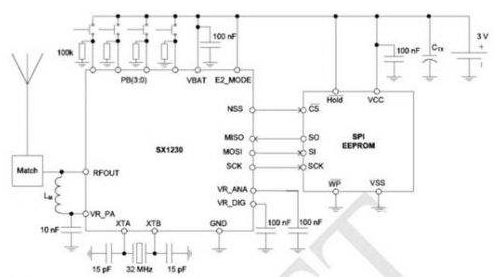

CMOS数字输出驱动器,在采样速率低于200 MSPS的ADC中,CMOS是很常见的数字输出。典型的CMOS驱动器由两个晶体管(一个NMOS和一个PMOS)组成,连接在电源(VDD)和地之间。这种结构会导致输出反转,背对背结构作为替代方法,避免输出反转。

ADC可以实现更高的动态范围。过采样的工作原理是假设噪声源不相关且均值为零,这是因为样本将白噪声视为频谱中均匀分布的噪声,或者将以相邻代码为中心的高斯噪声分布视为可通过平均来降低的信号。

使用AD7380所生成的快速傅立叶变换(FFT)曲线示例,分两种情况:无过采样和应用滚动平均过采样,OSR = 8。

利用AD7380改善噪声,本底噪声有显著改善,这与SNR的增加是一致的。在使能正常平均过采样和滚动平均过采样的情况下,SNR分别提高到96 dB和95 dB。

AD7380 SNR与过采样率的关系,要评估应用过采样技术所获得的SNR改善情况,请使用以下公式:

其中:

N为ADC分辨率。

fs为采样频率。

BW为目标带宽。

输出为低阻抗时,CMOS输出驱动器的输入为高阻抗。在驱动器的输入端,由于栅极与导电材料之间经栅极氧化层隔离,两个CMOS晶体管的栅极阻抗极高。输入端阻抗范围可达kΩ至MΩ级。在驱动器输出端,阻抗由漏电流ID控制,该电流通常较小。此时,阻抗通常小于几百Ω。CMOS的电平摆幅大约在VDD和地之间,因此可能会很大,具体取决于VDD幅度。

典型CMOS数字输出驱动器,由于输入阻抗较高,输出阻抗较低,CMOS的优势之一在于通常可以用一个输出驱动多个CMOS输入。CMOS的另一个优势是低静态电流。唯一出现较大电流的情况是CMOS驱动器上发生切换时。

无论驱动器处于低电平(拉至地)还是高电平(拉至VDD),驱动器中的电流都极小。但是,当驱动器从低电平切换到高电平或从高电平切换到低电平时,VDD与地之间会暂时出现低阻抗路径。

(素材来源:21ic.如涉版权请联系删除。特别感谢)

模数转换器(ADC)可以选择,数字数据输出类型是选择过程中需要考虑的一项重要参数。目前,高速转换器三种最常用的数字输出是互补金属氧化物半导体(CMOS)、低压差分信号(LVDS)和电流模式逻辑(CML)。ADC中每种数字输出类型都各有优劣,设计人员应根据特定应用仔细考虑。

这些因素取决于ADC的采样速率和分辨率、输出数据速率、系统设计的电源要求,以及其他因素。每种输出类型的电气规格,及其适合特定应用的具体特点。我们将从物理实现、效率以及最适合每种类型的应用这些方面来对比这些不同类型的输出。

CMOS数字输出驱动器,在采样速率低于200 MSPS的ADC中,CMOS是很常见的数字输出。典型的CMOS驱动器由两个晶体管(一个NMOS和一个PMOS)组成,连接在电源(VDD)和地之间。这种结构会导致输出反转,背对背结构作为替代方法,避免输出反转。

ADC可以实现更高的动态范围。过采样的工作原理是假设噪声源不相关且均值为零,这是因为样本将白噪声视为频谱中均匀分布的噪声,或者将以相邻代码为中心的高斯噪声分布视为可通过平均来降低的信号。

使用AD7380所生成的快速傅立叶变换(FFT)曲线示例,分两种情况:无过采样和应用滚动平均过采样,OSR = 8。

利用AD7380改善噪声,本底噪声有显著改善,这与SNR的增加是一致的。在使能正常平均过采样和滚动平均过采样的情况下,SNR分别提高到96 dB和95 dB。

AD7380 SNR与过采样率的关系,要评估应用过采样技术所获得的SNR改善情况,请使用以下公式:

其中:

N为ADC分辨率。

fs为采样频率。

BW为目标带宽。

输出为低阻抗时,CMOS输出驱动器的输入为高阻抗。在驱动器的输入端,由于栅极与导电材料之间经栅极氧化层隔离,两个CMOS晶体管的栅极阻抗极高。输入端阻抗范围可达kΩ至MΩ级。在驱动器输出端,阻抗由漏电流ID控制,该电流通常较小。此时,阻抗通常小于几百Ω。CMOS的电平摆幅大约在VDD和地之间,因此可能会很大,具体取决于VDD幅度。

典型CMOS数字输出驱动器,由于输入阻抗较高,输出阻抗较低,CMOS的优势之一在于通常可以用一个输出驱动多个CMOS输入。CMOS的另一个优势是低静态电流。唯一出现较大电流的情况是CMOS驱动器上发生切换时。

无论驱动器处于低电平(拉至地)还是高电平(拉至VDD),驱动器中的电流都极小。但是,当驱动器从低电平切换到高电平或从高电平切换到低电平时,VDD与地之间会暂时出现低阻抗路径。

(素材来源:21ic.如涉版权请联系删除。特别感谢)

上一篇:频率的速率对输入信号进行采样

公网安备44030402000607

公网安备44030402000607