频率较低或GDDR6吞吐量的数据

发布时间:2020/5/27 23:40:09 访问次数:432

MMA0204500.1BL1.8K为了实现高性能的算术运算,每个Speedster7t器件都具有一个大型可编程计算单元阵列,它们被有序地放置在机器学习处理器(MLP)单元模块中。MLP是一个高度可配置的计算密集型单元模块,在每个周期内可支持多达32个乘法/累加(MAC)运算。在以加速器为中心的设计中,MLP的存在使得在完全可编程逻辑和硬连线算术单元之间能够有效地共享资源。

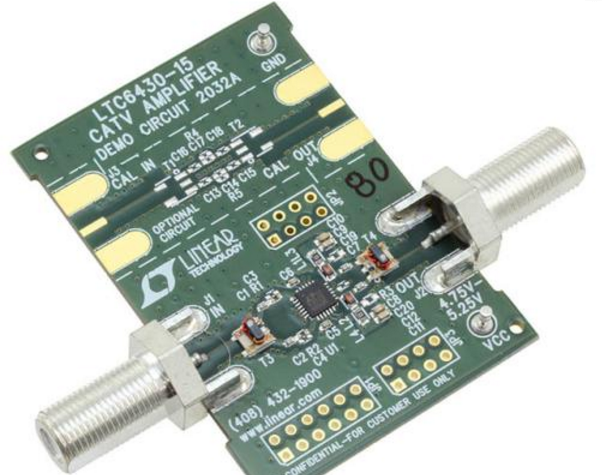

尽管有些FPGA倾向于使用HBM2存储器,其中FPGA和存储器被组装成一个昂贵的2.5D封装,而Speedster7t系列却采用GDDR6内存标准接口。这种接口提供了当今片外存储器可实现的最高性能,并且成本显著降低,从而使团队更容易去实现带有高带宽存储阵列的加速器。一个GDDR6存储控制器可以支持512 Gbps的带宽。VectorPath S7t-VG6加速卡可提供八组存储器,总存储带宽可以达到4 Tbps。此外,板上还有一个DDR4接口,可用于访问频率较低或不需要GDDR6吞吐量的数据。

VectorPath S7t-VG6加速卡提供了许多高性能接口,用来支持分布式架构和高速主机通信。现在,该加速卡提供了PCIe Gen 3.0的16通道合规性和认证,并提供获取Gen 4和Gen 5资质认证的途径。在以太网连接方面,该加速卡采用已获得广泛支持的光学接口模块,依据QSFP-DD和QSFP56标准,能够处理高达400 Gbps的超高线速。

在加速卡的另一端还有一个OCuLink扩展端口,以支持很多其他的低延迟应用场景。例如,OCuLink端口可用于将加速卡连接到各种外围设备上,比如用于计算存储或数据库加速应用的NVMe存储阵列。与采用连接到主处理器的PCIe接口相比,OCuLink连接能够成为一个更好的选择,因为它提供了一种消除了系统级延迟和抖动的高确定性的连接。OCuLink端口还可以引入其他网络连接,从而可扩展实现QSPF-DD或QSFP56之外的各种端口规格。

在VectorPath S7t-VG6加速卡的前面板上还包括多个时钟输入,它们是在将多个加速卡同步到一起时通常需要的。两个SMB时钟输入连接器支持从1PPS和10 MHz的时钟输入,它们在进入FPGA之前,就已被连接到抖动清除器。一旦进入FPGA,这些时钟就可以被倍频或分频成为特定应用所需的频率。

还可以通过通用数字I / O端头进行进一步扩展。该I / O端口支持单端3.3V连接和低电压差分(LVDS)信号,支持外部时钟、触发器和专用I / O等自定义信号直接连接到Speedster7t FPGA。该扩展端口还可用于将VectorPath加速卡改造为传统硬件。

VectorPath S7t-VG6加速卡已考虑到了每个细节,例如可支持被动和主动空气散热和液体散热。此外,BittWare和Achronix还为医疗等需要更长产品生命周期的领域确保提供长期的供应与支持。在这些市场中,基于GPU的PCIe加速卡较短的产品生命周期与超过10年的系统服务支持需求是不符的。

对于更大批量需求,特别是在边缘计算等场景中,客户可以使用BittWare的成本降低计划来简化硬件,其设计仅仅支持客户所需的I / O选项。此外,BittWare也可提供电路板设计文件以及VectorPath S7t-VG6加速卡随附的软件和驱动器的使用。利用Achronix的Speedcore eFPGA IP,也可以走向定制系统级芯片(SoC)器件。客户可以构建自己其中包括Speedster7t可编程性的SoC,但又具有ASIC的成本结构。

(素材来源:ttic和eechina.如涉版权请联系删除。特别感谢)

深圳市永拓丰科技有限公司http://ytf01.51dzw.com/

MMA0204500.1BL1.8K为了实现高性能的算术运算,每个Speedster7t器件都具有一个大型可编程计算单元阵列,它们被有序地放置在机器学习处理器(MLP)单元模块中。MLP是一个高度可配置的计算密集型单元模块,在每个周期内可支持多达32个乘法/累加(MAC)运算。在以加速器为中心的设计中,MLP的存在使得在完全可编程逻辑和硬连线算术单元之间能够有效地共享资源。

尽管有些FPGA倾向于使用HBM2存储器,其中FPGA和存储器被组装成一个昂贵的2.5D封装,而Speedster7t系列却采用GDDR6内存标准接口。这种接口提供了当今片外存储器可实现的最高性能,并且成本显著降低,从而使团队更容易去实现带有高带宽存储阵列的加速器。一个GDDR6存储控制器可以支持512 Gbps的带宽。VectorPath S7t-VG6加速卡可提供八组存储器,总存储带宽可以达到4 Tbps。此外,板上还有一个DDR4接口,可用于访问频率较低或不需要GDDR6吞吐量的数据。

VectorPath S7t-VG6加速卡提供了许多高性能接口,用来支持分布式架构和高速主机通信。现在,该加速卡提供了PCIe Gen 3.0的16通道合规性和认证,并提供获取Gen 4和Gen 5资质认证的途径。在以太网连接方面,该加速卡采用已获得广泛支持的光学接口模块,依据QSFP-DD和QSFP56标准,能够处理高达400 Gbps的超高线速。

在加速卡的另一端还有一个OCuLink扩展端口,以支持很多其他的低延迟应用场景。例如,OCuLink端口可用于将加速卡连接到各种外围设备上,比如用于计算存储或数据库加速应用的NVMe存储阵列。与采用连接到主处理器的PCIe接口相比,OCuLink连接能够成为一个更好的选择,因为它提供了一种消除了系统级延迟和抖动的高确定性的连接。OCuLink端口还可以引入其他网络连接,从而可扩展实现QSPF-DD或QSFP56之外的各种端口规格。

在VectorPath S7t-VG6加速卡的前面板上还包括多个时钟输入,它们是在将多个加速卡同步到一起时通常需要的。两个SMB时钟输入连接器支持从1PPS和10 MHz的时钟输入,它们在进入FPGA之前,就已被连接到抖动清除器。一旦进入FPGA,这些时钟就可以被倍频或分频成为特定应用所需的频率。

还可以通过通用数字I / O端头进行进一步扩展。该I / O端口支持单端3.3V连接和低电压差分(LVDS)信号,支持外部时钟、触发器和专用I / O等自定义信号直接连接到Speedster7t FPGA。该扩展端口还可用于将VectorPath加速卡改造为传统硬件。

VectorPath S7t-VG6加速卡已考虑到了每个细节,例如可支持被动和主动空气散热和液体散热。此外,BittWare和Achronix还为医疗等需要更长产品生命周期的领域确保提供长期的供应与支持。在这些市场中,基于GPU的PCIe加速卡较短的产品生命周期与超过10年的系统服务支持需求是不符的。

对于更大批量需求,特别是在边缘计算等场景中,客户可以使用BittWare的成本降低计划来简化硬件,其设计仅仅支持客户所需的I / O选项。此外,BittWare也可提供电路板设计文件以及VectorPath S7t-VG6加速卡随附的软件和驱动器的使用。利用Achronix的Speedcore eFPGA IP,也可以走向定制系统级芯片(SoC)器件。客户可以构建自己其中包括Speedster7t可编程性的SoC,但又具有ASIC的成本结构。

(素材来源:ttic和eechina.如涉版权请联系删除。特别感谢)

深圳市永拓丰科技有限公司http://ytf01.51dzw.com/

上一篇:功耗、电压和温度的监测程序

上一篇:集成的机架式机箱多核服务器

公网安备44030402000607

公网安备44030402000607