自动SMD组装系统贴片加工

发布时间:2020/5/27 19:45:58 访问次数:1177

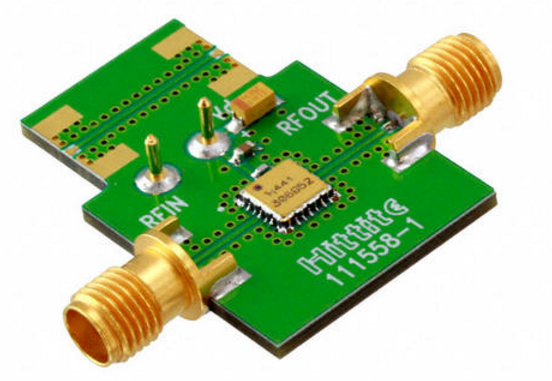

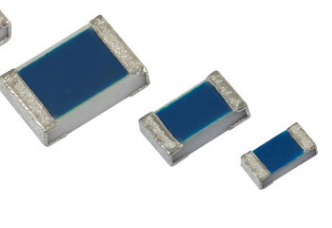

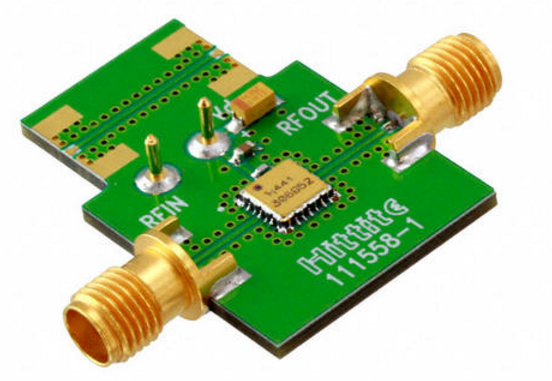

UM82C481BF温度系数(TCR)低至 2 ppm/K,0603、0805和1206外形尺寸新型器件,扩充其TNPU e3系列汽车级高精度薄膜扁平片式电阻。

Vishay Draloric TNPU e3系列电阻具有TNPW e3产品公认的可靠性并具有更高的精度,TCR低,公差不大于± 0.02 %,具有优异的长期稳定性―例如,在额定功率P70条件下,1,000小时最大阻值变化率≤ 0.05 %。这种独特技术特性使这款经过AEC Q200认证的电阻非常适合用于测试测量、汽车、工业、医疗和通信设备中运算放大器和传感器检测电路等应用。

TNPU e3系列器件TCR低至 2 ppm/K,外形尺寸分别为0603、0805和1206,阻值从500 到20 k。新款电阻具有出色的抗高温高湿性能(85 °C;85 % RH),耐硫性符合ASTM B 809标准,工作温度-55 °C至+125 °C,即使在恶劣环境下,也可以保证极为稳定的性能。

器件适用于自动SMD组装系统贴片加工,可使用自动波峰焊、回流焊或汽相再流焊。电阻符合RoHS标准,纯锡电镀兼容无铅(Pb)和含铅焊接工艺。

物联网AI、嵌入式视觉、硬件安全、5G通信、工业和汽车自动化等新兴应用正在重新定义开发人员设计网络边缘产品的硬件要求。为了支持这些应用,网络边缘设备的硬件方案需要具备下列特征:

低功耗

高性能

高稳定性

小尺寸

开始着手FPGA开发工艺的创新,旨在为客户提供具备上述特性的硬件平台。最终莱迪思成为业界首个支持28 nm全耗尽型绝缘体上硅(FD-SOI)工艺的低功耗FPGA供应商。该工艺由三星研发,与如今大多数半导体芯片采用的bulk CMOS工艺有些类似,但优势更为显著,能在显著降低器件尺寸和功耗的同时,大幅提升性能和稳定性。

支持全新的制造平台,莱迪思还依托其低功耗、小尺寸FPGA领先开发商的行业经验,在系统设计的各个层面(从完善的系统解决方案到FPGA架构,再到电路)取得创新,进一步降低功耗,减小FPGA尺寸,同时提升系统性能。全新的制造工艺与多个层面的创新催生了莱迪思Nexus™ FPGA开发平台。

有了Nexus FPGA技术平台,莱迪思可以通过集成更大的RAM和优化的DSP模块在本地存储数据和执行计算解决延迟问题。Nexus FPGA比之前的莱迪思FPGA性能提升了一倍(同时功耗降低一半),因此开发人员可以在网络边缘实现AI推理算法。网络边缘AI推理的潜在应用包括自动工业机器人、ADAS系统、安防摄像头和智能门铃等。

小尺寸不在话下,技术平台还能满足网络边缘设备不断精简尺寸的需求。许多FPGA厂商都在设计产品用于数据中心(云端)的数据分析应用,它们的架构很大,不适用于逻辑单元的数量较少的小型FPGA。莱迪思则专注开发小型、低功耗的FPGA,创造了紧凑的FPGA架构,其器件的物理尺寸比相似逻辑密度的FPGA竞品小十倍之多。莱迪思Nexus技术平台提供完善的系统解决方案。

除了Nexus技术平台上晶体管结构的创新之外,莱迪思还研究了设计过程中更高层次的抽象设计,以了解如何帮助客户在其应用设计中快速轻松地应用Nexus FPGA。莱迪思已经创建或购买并验证了易于使用、直观的设计软件、预先设计的软IP模块、评估板、套件以及完整的参考设计等资源,从而实现莱迪思目标市场(通信、计算、工业、汽车和消费电子)的各类常见应用,包括传感器聚合、传感器桥接和图像处理。

为嵌入式视觉市场提供完整的参考设计,让开发人员快速轻松地让新产品或现有产品设计支持流行的应用。

(素材来源:ttic和eechina.如涉版权请联系删除。特别感谢)

UM82C481BF温度系数(TCR)低至 2 ppm/K,0603、0805和1206外形尺寸新型器件,扩充其TNPU e3系列汽车级高精度薄膜扁平片式电阻。

Vishay Draloric TNPU e3系列电阻具有TNPW e3产品公认的可靠性并具有更高的精度,TCR低,公差不大于± 0.02 %,具有优异的长期稳定性―例如,在额定功率P70条件下,1,000小时最大阻值变化率≤ 0.05 %。这种独特技术特性使这款经过AEC Q200认证的电阻非常适合用于测试测量、汽车、工业、医疗和通信设备中运算放大器和传感器检测电路等应用。

TNPU e3系列器件TCR低至 2 ppm/K,外形尺寸分别为0603、0805和1206,阻值从500 到20 k。新款电阻具有出色的抗高温高湿性能(85 °C;85 % RH),耐硫性符合ASTM B 809标准,工作温度-55 °C至+125 °C,即使在恶劣环境下,也可以保证极为稳定的性能。

器件适用于自动SMD组装系统贴片加工,可使用自动波峰焊、回流焊或汽相再流焊。电阻符合RoHS标准,纯锡电镀兼容无铅(Pb)和含铅焊接工艺。

物联网AI、嵌入式视觉、硬件安全、5G通信、工业和汽车自动化等新兴应用正在重新定义开发人员设计网络边缘产品的硬件要求。为了支持这些应用,网络边缘设备的硬件方案需要具备下列特征:

低功耗

高性能

高稳定性

小尺寸

开始着手FPGA开发工艺的创新,旨在为客户提供具备上述特性的硬件平台。最终莱迪思成为业界首个支持28 nm全耗尽型绝缘体上硅(FD-SOI)工艺的低功耗FPGA供应商。该工艺由三星研发,与如今大多数半导体芯片采用的bulk CMOS工艺有些类似,但优势更为显著,能在显著降低器件尺寸和功耗的同时,大幅提升性能和稳定性。

支持全新的制造平台,莱迪思还依托其低功耗、小尺寸FPGA领先开发商的行业经验,在系统设计的各个层面(从完善的系统解决方案到FPGA架构,再到电路)取得创新,进一步降低功耗,减小FPGA尺寸,同时提升系统性能。全新的制造工艺与多个层面的创新催生了莱迪思Nexus™ FPGA开发平台。

有了Nexus FPGA技术平台,莱迪思可以通过集成更大的RAM和优化的DSP模块在本地存储数据和执行计算解决延迟问题。Nexus FPGA比之前的莱迪思FPGA性能提升了一倍(同时功耗降低一半),因此开发人员可以在网络边缘实现AI推理算法。网络边缘AI推理的潜在应用包括自动工业机器人、ADAS系统、安防摄像头和智能门铃等。

小尺寸不在话下,技术平台还能满足网络边缘设备不断精简尺寸的需求。许多FPGA厂商都在设计产品用于数据中心(云端)的数据分析应用,它们的架构很大,不适用于逻辑单元的数量较少的小型FPGA。莱迪思则专注开发小型、低功耗的FPGA,创造了紧凑的FPGA架构,其器件的物理尺寸比相似逻辑密度的FPGA竞品小十倍之多。莱迪思Nexus技术平台提供完善的系统解决方案。

除了Nexus技术平台上晶体管结构的创新之外,莱迪思还研究了设计过程中更高层次的抽象设计,以了解如何帮助客户在其应用设计中快速轻松地应用Nexus FPGA。莱迪思已经创建或购买并验证了易于使用、直观的设计软件、预先设计的软IP模块、评估板、套件以及完整的参考设计等资源,从而实现莱迪思目标市场(通信、计算、工业、汽车和消费电子)的各类常见应用,包括传感器聚合、传感器桥接和图像处理。

为嵌入式视觉市场提供完整的参考设计,让开发人员快速轻松地让新产品或现有产品设计支持流行的应用。

(素材来源:ttic和eechina.如涉版权请联系删除。特别感谢)

上一篇:触发源的选择操作和选择数字通道

上一篇:28 nm全耗尽型绝缘体上硅

热门点击

热门点击

- 差模滤波和共模滤波电路

- 振荡器相位噪声分析仪

- 分立半导体数据包目标模块

- 测试设备和仪器高度优化

- I/O接口及高可靠性数据传输

- 产品的漏源导通电阻降低

- 抑制周期性的干扰平滑度差

- 有源箝位驱动器和启动调节器

- 开关损耗和碳化硅场效应晶体管

- 开关损耗的周期式过流过温保护和负载开短路

推荐技术资料

推荐技术资料

- 中国传媒大学传媒博物馆开

- 传媒博物馆开馆仪式隆童举行。教育都i国家广电总局等部门... [详细]

公网安备44030402000607

公网安备44030402000607