XRD4411AID 控制逻辑电路自动屏蔽输出信号

发布时间:2020/2/10 20:00:07 访问次数:939

A-B≥0的情况。设A=0101,B=0001。

求补相加演算过程如下:

个(借位)直接作减法演算,则有比较两种运算结果,它们完的原码,借位信号为0。

A-B(0的情况。设A求补相加演算过程如下:

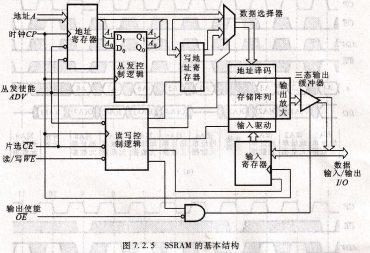

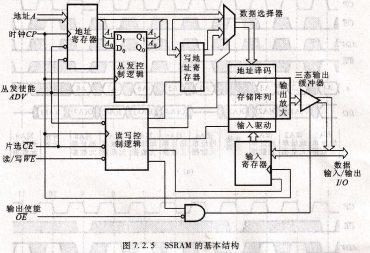

(借位)直接作减法演算,则有表示行变全相同。在A-B≥0时,所得的差值就是差(进位反相)式输出,则成输出为原异或门的,一地址码读写控制逻辑丛发控逻辑,写地址寄存器输出放大输入驱动时式读写。读/写控制信号WE低电平为写操作,高电平为读操作。

数据选择器丛发,便能为D7三态输出缓冲器片,选CE数据输入/输出f/o输出使oE能图7.2.5 ssRAM的基本结构.

读操作时,控制信号和地址输人在CP的上升沿被取样,当丛发使能控制ADy和片选CE为低电平时,地址线上的地址被锁存到地址寄存器中,高电平的WE也被寄存到读写控制逻辑电路中。此时,读写控制逻辑电路使数据选择器选择地址寄存器中的地址进行译码,在下一个CP有效沿到来前,存储阵列中的数据被送到数据线f/o上输出。操作过程如图7.2.6(a)所示。

写操作与读操作类似,只是被取样的WE为低电平。而输人的数据在接下来的CP上升沿锁存到输人寄存器中,同时地址寄存器中的地址又传至写地址寄存器中。此时,读写控制逻辑电路使数据选择器选择写地址寄存器中的地址进行译码,在输入驱动电路的作用下,将输人寄存器中的数据写人存储阵列。写操作时,读写控制逻辑电路将自动屏蔽输出使能信号oE,使三态输出缓冲器呈现高阻态。操作过程如图7.2.6(a)所示。

丛发模式读写操作是sSRAM中特有的①。当丛发使能控制且D/为低电平时,A1A。可直接穿过丛发控制逻辑电路,按外部给定的地址进行读/写,此时就是上述的一般读写操作。但当丛发使能控制ADy为高电平时,地址寄存器不接收外部新地址而保持上一个时钟周期输人的地址,在CP下一个上升沿到随视存取存储器.不仅SSRAM中有丛发模式,而且sDRAM中也有该模式。

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

A-B≥0的情况。设A=0101,B=0001。

求补相加演算过程如下:

个(借位)直接作减法演算,则有比较两种运算结果,它们完的原码,借位信号为0。

A-B(0的情况。设A求补相加演算过程如下:

(借位)直接作减法演算,则有表示行变全相同。在A-B≥0时,所得的差值就是差(进位反相)式输出,则成输出为原异或门的,一地址码读写控制逻辑丛发控逻辑,写地址寄存器输出放大输入驱动时式读写。读/写控制信号WE低电平为写操作,高电平为读操作。

数据选择器丛发,便能为D7三态输出缓冲器片,选CE数据输入/输出f/o输出使oE能图7.2.5 ssRAM的基本结构.

读操作时,控制信号和地址输人在CP的上升沿被取样,当丛发使能控制ADy和片选CE为低电平时,地址线上的地址被锁存到地址寄存器中,高电平的WE也被寄存到读写控制逻辑电路中。此时,读写控制逻辑电路使数据选择器选择地址寄存器中的地址进行译码,在下一个CP有效沿到来前,存储阵列中的数据被送到数据线f/o上输出。操作过程如图7.2.6(a)所示。

写操作与读操作类似,只是被取样的WE为低电平。而输人的数据在接下来的CP上升沿锁存到输人寄存器中,同时地址寄存器中的地址又传至写地址寄存器中。此时,读写控制逻辑电路使数据选择器选择写地址寄存器中的地址进行译码,在输入驱动电路的作用下,将输人寄存器中的数据写人存储阵列。写操作时,读写控制逻辑电路将自动屏蔽输出使能信号oE,使三态输出缓冲器呈现高阻态。操作过程如图7.2.6(a)所示。

丛发模式读写操作是sSRAM中特有的①。当丛发使能控制且D/为低电平时,A1A。可直接穿过丛发控制逻辑电路,按外部给定的地址进行读/写,此时就是上述的一般读写操作。但当丛发使能控制ADy为高电平时,地址寄存器不接收外部新地址而保持上一个时钟周期输人的地址,在CP下一个上升沿到随视存取存储器.不仅SSRAM中有丛发模式,而且sDRAM中也有该模式。

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

公网安备44030402000607

公网安备44030402000607