HY62256ALG-70 ����оƬ�������з�ʽ��˫��ֱ��ʽ

����ʱ��:2020/2/10 18:57:58 ���ʴ���:1061

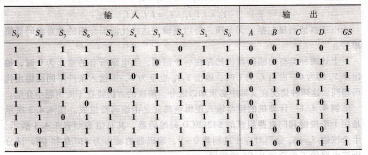

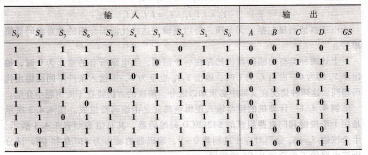

HY62256ALG-70�����������ܼ�Ӧ��:����ֵ��������·���з���,�ɵ�֪:�ٸñ�����Ϊ����͵�ƽ��Ч;���ڰ���s��~S9������һ����ʱ,�������ź�����һ��Ϊ�͵�ƽʱCs=1,��ʾ���ź�����,��ֻ��sO~s9��Ϊ�ߵ�ƽʱCs=0,��ʾ���ź�����,��ʱ���������0000Ϊ��Ч���롣�ɴ˽����ͼ4,4,1��ʾ��·���ڵ�����.

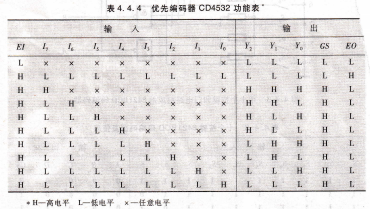

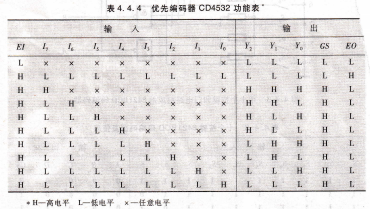

Hһ�ߵ�ƽ Lһ�͵�ƽ ��һ�����ƽ

�ӹ��ܱ����Կ���,�ñ�������8���ź������,3���������������,���˺�������Ըߵ�ƽ��Ϊ��Ч��ƽ,�����������ȼ���Ĵ�������Ϊr7,f6,,JO������Ϊ���ڶ��оƬ����������չ��·�Ĺ���,�������˸ߵ�ƽ��Ч������ʹ�ܶ�Er�����ʹ�ܶ�Eo,�Լ����ȱ��빤��״̬��־Cs��

��EJ=1��ʱ,����������;����Er=oʱ,��ֹ����������,��ʱ����8�����˶�Ϊ����״̬,3������˾�Ϊ�͵�ƽ,��Cs��EO��Ϊ�͵�ƽ��E0ֻ����ErΪ1,���������˶˶�Ϊ0ʱ,���Ϊ1,��������һƬ��ͬ������Er����,�Ա���ɸ�������˵����ȱ�������

Cs�Ĺ�����,��EJΪ1,��������һ�����˶��иߵ�ƽ�ź�����ʱ,CsΪ1,�������������ڹ���״̬,����CsΪ0,�ɴ˿������ֵ���·�������˶˾��ߵ�ƽ����,����ֻ�м�������иߵ�ƽʱ,�yl���Ϊ000����������ܱ�����1��0�ֱ��ʾ�ߡ��͵�ƽ,�Ƶ���������˵�������ʽ��

y^=Ef f7f6r5 r4 (4.4.1)

y1=Er f7J6(f5+J4+f3)(+r4+)

yl=Er(J6+f5)(k+r3)(j+f4+r2+rl)

Er`=Er(7J6f5r3J1fO)

EC9=Er+J7+J6+r5+f4+r3+J2+rt+ro

Cs=Er+Er(J7f6f5��Ja J2 J1��)

cs=Er.f6f5r3J1 (4・4・5)

��ʽ(4.4,1)~ʽ(4.4,5)������ͼ,��ͼ4.4.4(a)��ʾ,CD4532�����ںź�����ͼ�ֱ���ͼ4.4.4(b)��ͼ4.4.4(c)��ʾ������оƬ���ŵ��������з�ʽ��Ϊ˫��ֱ��ʽ��װ������ͨ������˵��8��һ3�߱�������Ӧ�á���4.4.2 ����ƬCD4532���16��һ4�����ȱ�����,����ͼ��ͼ4.4.5��ʾ,�Է����乤��ԭ����

��:����CD4532�Ĺ��ܱ�,����ͼ���з����ó�:

�ٵ���1=0ʱ,Ƭ(1)��ֹ����,��������yl yOΪ000,����Cs1��E91��Ϊ0��ͬʱE91ʹE��=0,Ƭ(0)Ҳ��ֹ����,������˼�CsO��Eo0��Ϊ0���ɵ�·ͼ��֪Cs=Cs��+Csl=0,��ʾ��ʱ������·�Ĵ��������

Z3L2L1��=0000�ǷDZ��������

��Er1=1ʱ,Ƭ(1)��������,��A15~A:������Ч��ƽ����,��EO1=1,ʹEr��=1,�Ӷ�����Ƭ(0)����,���Ƭ(1)�����ȼ�����Ƭ(0)��

��ʱ����A15��A:û����Ч��ƽ����ʱ,Ƭ(1)�������Ϊ0~ʹ4������0���ܱ����øߡ��͵�ƽ��ʾ.����ʱ��������ĵ����,HI��0�ֱ��ʾ���ϵ����ɵ��͵��ܺ������ɵ�·.

������Ψ�жȿƼ�����˾http://wydkj.51dzw.com/

HY62256ALG-70�����������ܼ�Ӧ��:����ֵ��������·���з���,�ɵ�֪:�ٸñ�����Ϊ����͵�ƽ��Ч;���ڰ���s��~S9������һ����ʱ,�������ź�����һ��Ϊ�͵�ƽʱCs=1,��ʾ���ź�����,��ֻ��sO~s9��Ϊ�ߵ�ƽʱCs=0,��ʾ���ź�����,��ʱ���������0000Ϊ��Ч���롣�ɴ˽����ͼ4,4,1��ʾ��·���ڵ�����.

Hһ�ߵ�ƽ Lһ�͵�ƽ ��һ�����ƽ

�ӹ��ܱ����Կ���,�ñ�������8���ź������,3���������������,���˺�������Ըߵ�ƽ��Ϊ��Ч��ƽ,�����������ȼ���Ĵ�������Ϊr7,f6,,JO������Ϊ���ڶ��оƬ����������չ��·�Ĺ���,�������˸ߵ�ƽ��Ч������ʹ�ܶ�Er�����ʹ�ܶ�Eo,�Լ����ȱ��빤��״̬��־Cs��

��EJ=1��ʱ,����������;����Er=oʱ,��ֹ����������,��ʱ����8�����˶�Ϊ����״̬,3������˾�Ϊ�͵�ƽ,��Cs��EO��Ϊ�͵�ƽ��E0ֻ����ErΪ1,���������˶˶�Ϊ0ʱ,���Ϊ1,��������һƬ��ͬ������Er����,�Ա���ɸ�������˵����ȱ�������

Cs�Ĺ�����,��EJΪ1,��������һ�����˶��иߵ�ƽ�ź�����ʱ,CsΪ1,�������������ڹ���״̬,����CsΪ0,�ɴ˿������ֵ���·�������˶˾��ߵ�ƽ����,����ֻ�м�������иߵ�ƽʱ,�yl���Ϊ000����������ܱ�����1��0�ֱ��ʾ�ߡ��͵�ƽ,�Ƶ���������˵�������ʽ��

y^=Ef f7f6r5 r4 (4.4.1)

y1=Er f7J6(f5+J4+f3)(+r4+)

yl=Er(J6+f5)(k+r3)(j+f4+r2+rl)

Er`=Er(7J6f5r3J1fO)

EC9=Er+J7+J6+r5+f4+r3+J2+rt+ro

Cs=Er+Er(J7f6f5��Ja J2 J1��)

cs=Er.f6f5r3J1 (4・4・5)

��ʽ(4.4,1)~ʽ(4.4,5)������ͼ,��ͼ4.4.4(a)��ʾ,CD4532�����ںź�����ͼ�ֱ���ͼ4.4.4(b)��ͼ4.4.4(c)��ʾ������оƬ���ŵ��������з�ʽ��Ϊ˫��ֱ��ʽ��װ������ͨ������˵��8��һ3�߱�������Ӧ�á���4.4.2 ����ƬCD4532���16��һ4�����ȱ�����,����ͼ��ͼ4.4.5��ʾ,�Է����乤��ԭ����

��:����CD4532�Ĺ��ܱ�,����ͼ���з����ó�:

�ٵ���1=0ʱ,Ƭ(1)��ֹ����,��������yl yOΪ000,����Cs1��E91��Ϊ0��ͬʱE91ʹE��=0,Ƭ(0)Ҳ��ֹ����,������˼�CsO��Eo0��Ϊ0���ɵ�·ͼ��֪Cs=Cs��+Csl=0,��ʾ��ʱ������·�Ĵ��������

Z3L2L1��=0000�ǷDZ��������

��Er1=1ʱ,Ƭ(1)��������,��A15~A:������Ч��ƽ����,��EO1=1,ʹEr��=1,�Ӷ�����Ƭ(0)����,���Ƭ(1)�����ȼ�����Ƭ(0)��

��ʱ����A15��A:û����Ч��ƽ����ʱ,Ƭ(1)�������Ϊ0~ʹ4������0���ܱ����øߡ��͵�ƽ��ʾ.����ʱ��������ĵ����,HI��0�ֱ��ʾ���ϵ����ɵ��͵��ܺ������ɵ�·.

������Ψ�жȿƼ�����˾http://wydkj.51dzw.com/

�������

�������

- TDSG-5150�������ݵ�ʧЧ�ͷ���������

- Q4739125 ���ɲ���ʹ�ÿ��������ɽ���

- NMC27CP128Q200 ��Ƶ��Ӧ������

- LSD5114-10 ������Ƥ�ĸ��ȴ�������

- STM32F105VBT6 �������2������

- TL3844D-8 �������Ż����¶Ȳ���

- SFSCE10M7WF03-R0 ��ͨ�˲���

- SKP70N06���Ӻ������ӵĵ�ų������

- SKBT40/08 ���ʽ���ذ������ڶ�����

- XCV200-5FG256CES���߳�������

�Ƽ���������

�Ƽ���������

- ��ť��ƵĻ���ʵ��

- ���ڸϿ�ȥ�������Ŀ¼����ʲô��FGA15N120AN... [��ϸ]

- �߷��ӻ������������Ӧ��̽��

- ��Ч����4kW˫��PFC��Դ�������

- ��ɢ�뵼��Ԫ��������ܡ�������

- CommonGround Human AI&

- 520�߳��漶���ֻ������״�Ӧ

- MPronto-12 (M12

- ��ý��Э������SM501��Ƕ��ʽϵͳ�е�Ӧ��

- ����IEEE802.11b��EPA�¶ȱ�����

- QUICCEngine�������ƶ�IP�������

- SoC���������IJ�ҵ����

- MPC8xxϵ�д�������Ƕ��ʽϵͳ��Դ���

- dsPIC�����ڽ�����Ƶ�����е�Ӧ���о�

��������44030402000607

��������44030402000607