ATMEGA8-8PU 砷化镓器件最突出的优点

发布时间:2020/2/9 16:30:17 访问次数:1505

ATMEGA8-8PU门电路接口,就要用专门的电平移动电路。

双极型逻辑门电路除了TTL和ECL之外,尚有集成注入逻辑门电路(IIL①或I2L)和高阈值逻辑门电路(HTL②)。由于IIL电路简单,易于在硅片上实现高集成度的器件,因而它在大规模和超大规模集成电路中得到应用,但不制成单个集成门电路。由于它的高、低电平电压差值很小,抗干扰能力较差,因而这种门电路的推广受到限制。至于HTL,虽然它有较强的抗干扰能力,但它的功耗大,开关速度也不高,已不生产。

ECL门电路为什么具有很高的开关速度?该类电路有什么特点?

由GaAs材料制成的N沟道场效应管,称为金属一半导体场效应管(MES-FET)。它的栅极金属与N沟道表面接触形成肖特基势垒区,与硅JFET中栅极与沟道间的PN结类似,工作原理也类似。由于砷化镓器件中载流子的迁移率非常高,因而其工作速度比硅器件快得多。在MESFET管构成的逻辑电路中,应用较多的有直接耦合FET逻辑门电路、耗尽型FET逻辑门电路以及肖特基二极管FET逻辑门电路。

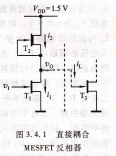

直接耦合FET逻辑电路,由MESFET管组成的直接耦合FET反相器如图.

3.4.1所示,图中增强型管T1为工作管,耗尽型管vIT2为负载管,下一级门电路的T3作为负载。增强型管的开启电压uE为0.1~0.3Ⅴ;耗尽型管的夹断电压uD为=0.7~0.1V。由于栅极和沟道间存在肖特.

图3.4.1 直接耦合,基势垒二极管,使MESFET管导通时的栅源电压vcs MESFET反相器为0.7Ⅴ。该电路输入信号的高、低电平分别为0.63Ⅴ和0.54V;输出信号的高、低电平分别为0.7Ⅴ和0.17V。

IIL系Integrated jection Logic的缩写。

HTL系High-Threshol Logic的缩写。

2yD+vGs4=2.IV,输出为高电平。当输入增加到vI≥D时,T1管导通,但最初吒仍为2.1V,使T1管工作在饱和区,并产生漏极电流J1,致使流入T4管电流L减少。但T4仍然导通,则输出电压的值仍接近于0.7V。当v增加至-0.26Ⅴ时,j1+j3=J2,使jL=0,T4截止。

继续增加vI,吒下降使u>vio+|uD|时,T1进入可变电阻区,输出电压约为0,17V。此时,T2和T3仍工作在饱和区,D1、D2保持导通,uo=-2+3=-1.23Ⅴ。当输人达到高电平电压-0.16Ⅴ以后,输出电压下降到-1.27V的低电平。

上述输入、输出转折点的电压值,可以根据MESFET工作在不同区域时的JD与vGs及Ds关系进行计算,详细内容可以参阅参考文献[1]。

耗尽型MESFET逻辑电路的噪声容限比直接耦合逻辑电路的噪声容限高,但电路要求两个供电电源。

砷化镓器件最突出的优点是工作速度比硅器仵快得多,门传输延迟时间为10~100 ps。其缺点是功耗较大,逻辑摆幅小,因此噪声容限低,抗干扰能力较差。目前砷化镓技术主要用于小规模、中规模和大规模集成电路的生产。

为什么砷化镓器件比硅器件速度快,现在应用较多的有哪几种类型的逻辑电路?

正负逻辑问题,正负逻辑的规定,在数字电路中,可以采用两种不同的逻辑体制表示电路输人和输出的高、

低电平。在前面讨论时,将高电平用逻辑1表示,低电平用逻辑0表示,这种表示方法称为正逻辑体制。如果将高电平用逻辑0表示,低电平用逻辑1表示,则这种表示方法称为负逻辑体制。

对于同一电路的输入与输出关系的描述,可以采用正逻辑,也可以采用负逻辑描述中的几个问题.

ATMEGA8-8PU门电路接口,就要用专门的电平移动电路。

双极型逻辑门电路除了TTL和ECL之外,尚有集成注入逻辑门电路(IIL①或I2L)和高阈值逻辑门电路(HTL②)。由于IIL电路简单,易于在硅片上实现高集成度的器件,因而它在大规模和超大规模集成电路中得到应用,但不制成单个集成门电路。由于它的高、低电平电压差值很小,抗干扰能力较差,因而这种门电路的推广受到限制。至于HTL,虽然它有较强的抗干扰能力,但它的功耗大,开关速度也不高,已不生产。

ECL门电路为什么具有很高的开关速度?该类电路有什么特点?

由GaAs材料制成的N沟道场效应管,称为金属一半导体场效应管(MES-FET)。它的栅极金属与N沟道表面接触形成肖特基势垒区,与硅JFET中栅极与沟道间的PN结类似,工作原理也类似。由于砷化镓器件中载流子的迁移率非常高,因而其工作速度比硅器件快得多。在MESFET管构成的逻辑电路中,应用较多的有直接耦合FET逻辑门电路、耗尽型FET逻辑门电路以及肖特基二极管FET逻辑门电路。

直接耦合FET逻辑电路,由MESFET管组成的直接耦合FET反相器如图.

3.4.1所示,图中增强型管T1为工作管,耗尽型管vIT2为负载管,下一级门电路的T3作为负载。增强型管的开启电压uE为0.1~0.3Ⅴ;耗尽型管的夹断电压uD为=0.7~0.1V。由于栅极和沟道间存在肖特.

图3.4.1 直接耦合,基势垒二极管,使MESFET管导通时的栅源电压vcs MESFET反相器为0.7Ⅴ。该电路输入信号的高、低电平分别为0.63Ⅴ和0.54V;输出信号的高、低电平分别为0.7Ⅴ和0.17V。

IIL系Integrated jection Logic的缩写。

HTL系High-Threshol Logic的缩写。

2yD+vGs4=2.IV,输出为高电平。当输入增加到vI≥D时,T1管导通,但最初吒仍为2.1V,使T1管工作在饱和区,并产生漏极电流J1,致使流入T4管电流L减少。但T4仍然导通,则输出电压的值仍接近于0.7V。当v增加至-0.26Ⅴ时,j1+j3=J2,使jL=0,T4截止。

继续增加vI,吒下降使u>vio+|uD|时,T1进入可变电阻区,输出电压约为0,17V。此时,T2和T3仍工作在饱和区,D1、D2保持导通,uo=-2+3=-1.23Ⅴ。当输人达到高电平电压-0.16Ⅴ以后,输出电压下降到-1.27V的低电平。

上述输入、输出转折点的电压值,可以根据MESFET工作在不同区域时的JD与vGs及Ds关系进行计算,详细内容可以参阅参考文献[1]。

耗尽型MESFET逻辑电路的噪声容限比直接耦合逻辑电路的噪声容限高,但电路要求两个供电电源。

砷化镓器件最突出的优点是工作速度比硅器仵快得多,门传输延迟时间为10~100 ps。其缺点是功耗较大,逻辑摆幅小,因此噪声容限低,抗干扰能力较差。目前砷化镓技术主要用于小规模、中规模和大规模集成电路的生产。

为什么砷化镓器件比硅器件速度快,现在应用较多的有哪几种类型的逻辑电路?

正负逻辑问题,正负逻辑的规定,在数字电路中,可以采用两种不同的逻辑体制表示电路输人和输出的高、

低电平。在前面讨论时,将高电平用逻辑1表示,低电平用逻辑0表示,这种表示方法称为正逻辑体制。如果将高电平用逻辑0表示,低电平用逻辑1表示,则这种表示方法称为负逻辑体制。

对于同一电路的输入与输出关系的描述,可以采用正逻辑,也可以采用负逻辑描述中的几个问题.

公网安备44030402000607

公网安备44030402000607