TMS320LC31PQL40同步计数器

发布时间:2019/10/18 22:53:39 访问次数:808

TMS320LC31PQL40计数器运行时总是从某个起始状态开始,依次经过所有不重复的状态后完成一次循环。把一次循环所包含的状态数称为计数器的“模”.用Ⅲ表示。1r系Modulo的字头。

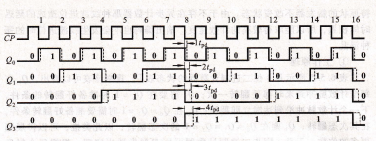

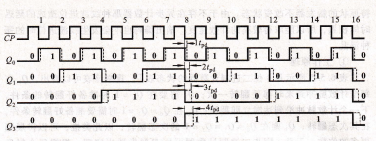

异步二进制计数器的原理、结构简单,因各触发器不是同时翻转,而是逐级脉动翻转实现计数进位的,故亦称为纹波计数器①。图6.5.9中的虚线是考虑了触发器逐级翻转中平均传输延迟时间rpd的波形。由于各触发器的翻转时间有延迟,若用该计数器驱动组合逻辑电路,则可能出现瞬间逻辑错误。例如,当计数值从0111加1时,先后要经过0110、0100、0000几个状态,才最终翻转为1000。如果对0110、0100、0000译码,这时译码输出端则会出现毛刺状波形。另外,当计数脉冲频率很高时,03~0。甚至会出现编码输出分辨不清的情况。对于一个Ⅳ位二进制异步计数器来说,从一个计数脉冲开始作用到第一个触发器,到第Ⅳ个触发器翻转达到稳定状态,需要经历的时间为``rrpd。为了保证正确地检出计数器的输出状态,必须满足rcP>>助pd的条件,其中,rcP为计数脉冲CP的周期。

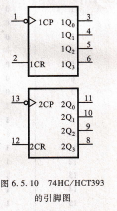

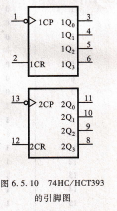

典型集成电路,中规模集成电路74HC/HCT393中集成了两个如图6.5.8所示的4位异步二进制计数器,图6.5.10所示是它的引脚图。在5Ⅴ、25℃工作条件下,74HC/HCT393中每级触发器传输延迟时间的典型值为6ns。

同步二进制加计数器,为了提高计数速度,可采用同步计数器。其特点是,计数脉冲作为时钟信号同时接于各位触发器的时图6.5.10 74HC/HCT393钟脉冲输入端,在每次时钟脉冲沿到来之前,根据当的引脚图前计数器状态,利用组合逻辑控制,准各好适当的条件。当计数脉冲沿到来时,所有应翻转的触发器同时翻转,同时也使所有应保持原状的触发器不改变状态。由于不存在异步计数器那种纹波进位造成的延迟时间积累,所以能取得较高的计数速度,输出编码也不会发生纹波进位时的那种混乱。

TMS320LC31PQL40计数器运行时总是从某个起始状态开始,依次经过所有不重复的状态后完成一次循环。把一次循环所包含的状态数称为计数器的“模”.用Ⅲ表示。1r系Modulo的字头。

异步二进制计数器的原理、结构简单,因各触发器不是同时翻转,而是逐级脉动翻转实现计数进位的,故亦称为纹波计数器①。图6.5.9中的虚线是考虑了触发器逐级翻转中平均传输延迟时间rpd的波形。由于各触发器的翻转时间有延迟,若用该计数器驱动组合逻辑电路,则可能出现瞬间逻辑错误。例如,当计数值从0111加1时,先后要经过0110、0100、0000几个状态,才最终翻转为1000。如果对0110、0100、0000译码,这时译码输出端则会出现毛刺状波形。另外,当计数脉冲频率很高时,03~0。甚至会出现编码输出分辨不清的情况。对于一个Ⅳ位二进制异步计数器来说,从一个计数脉冲开始作用到第一个触发器,到第Ⅳ个触发器翻转达到稳定状态,需要经历的时间为``rrpd。为了保证正确地检出计数器的输出状态,必须满足rcP>>助pd的条件,其中,rcP为计数脉冲CP的周期。

典型集成电路,中规模集成电路74HC/HCT393中集成了两个如图6.5.8所示的4位异步二进制计数器,图6.5.10所示是它的引脚图。在5Ⅴ、25℃工作条件下,74HC/HCT393中每级触发器传输延迟时间的典型值为6ns。

同步二进制加计数器,为了提高计数速度,可采用同步计数器。其特点是,计数脉冲作为时钟信号同时接于各位触发器的时图6.5.10 74HC/HCT393钟脉冲输入端,在每次时钟脉冲沿到来之前,根据当的引脚图前计数器状态,利用组合逻辑控制,准各好适当的条件。当计数脉冲沿到来时,所有应翻转的触发器同时翻转,同时也使所有应保持原状的触发器不改变状态。由于不存在异步计数器那种纹波进位造成的延迟时间积累,所以能取得较高的计数速度,输出编码也不会发生纹波进位时的那种混乱。

公网安备44030402000607

公网安备44030402000607