STC11F52XE-35I-L 循环的控制条件

发布时间:2019/10/16 21:13:54 访问次数:1111

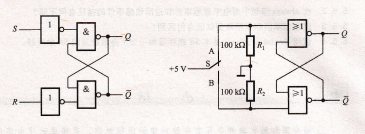

STC11F52XE-35I-L触发器的逻辑功能和电路结构之间有什么关系?

写出D触发器、JK触发器、r触发器和SR触发器的特性方程,并画出它们的状态图.

怎样利用JK触发器实现9触发器、'触发器、r`以及s灾触发器的逻辑功能?

对组合逻辑电路的行为级建模进行了简单介绍,本节将讨论时序电路的基本部件一锁存器和触发器的建模,首先介绍有关的基础知识,然后以实例进行说明。

时序电路建模基础,在Verilog中,行为级描述主要使用由关键词inidal或always定义的两种结构类型的语句。一个模块的内部可以包含多个inidal或anways语句,仿真时这些语句同时并行执行,即与它们在模块内部排列的顺序无关,都从仿真的0时刻开始执行。

inmial语句是一条初始化语句,仅执行一次,经常用于测试模块中对激励信号进行描述,在硬件电路的行为描述中,有时为了仿真的需要,也用inmal语句给寄存器变量赋初值。inmal语句主要是一条面向仿真的过程语句,不能用于逻辑综合,因而本书将不作详细介绍。

always本身是一个无限循环语句,即不停地循环执行其内部的过程语句,直到仿真过程结束。但用它来描述硬件电路的逻辑功能时,通常在always后面紧跟着循环的控制条件,所以always语句的一般用法如下:

always@(事件控制表达式)

begin

块内局部变量的定义;

过程赋值语句;

end

这里,“事件控制表达式”也称为敏感事件表,即等待确定的事件发生或某一特定的条件变为“真”,它是执行后面过程赋值语句的条件。“过程赋值语句”左边的变量必须被定义成寄存器数据类型,右边变量可以是任意数据类型。beˉgin和end将多条过程赋值语句包围起来,组成一个顺序语句块,块内的语句按照排列顺序依次执行,最后一条语句执行完后,执行挂起,然后anways语句处于等待状态,等待下一个事件的发生。注意,当begin和end之间只有一条语句,且没有定义局部变量时,则关键词begin和end可以被省略。

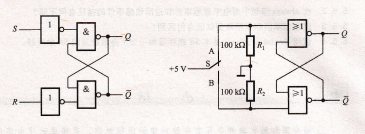

STC11F52XE-35I-L触发器的逻辑功能和电路结构之间有什么关系?

写出D触发器、JK触发器、r触发器和SR触发器的特性方程,并画出它们的状态图.

怎样利用JK触发器实现9触发器、'触发器、r`以及s灾触发器的逻辑功能?

对组合逻辑电路的行为级建模进行了简单介绍,本节将讨论时序电路的基本部件一锁存器和触发器的建模,首先介绍有关的基础知识,然后以实例进行说明。

时序电路建模基础,在Verilog中,行为级描述主要使用由关键词inidal或always定义的两种结构类型的语句。一个模块的内部可以包含多个inidal或anways语句,仿真时这些语句同时并行执行,即与它们在模块内部排列的顺序无关,都从仿真的0时刻开始执行。

inmial语句是一条初始化语句,仅执行一次,经常用于测试模块中对激励信号进行描述,在硬件电路的行为描述中,有时为了仿真的需要,也用inmal语句给寄存器变量赋初值。inmal语句主要是一条面向仿真的过程语句,不能用于逻辑综合,因而本书将不作详细介绍。

always本身是一个无限循环语句,即不停地循环执行其内部的过程语句,直到仿真过程结束。但用它来描述硬件电路的逻辑功能时,通常在always后面紧跟着循环的控制条件,所以always语句的一般用法如下:

always@(事件控制表达式)

begin

块内局部变量的定义;

过程赋值语句;

end

这里,“事件控制表达式”也称为敏感事件表,即等待确定的事件发生或某一特定的条件变为“真”,它是执行后面过程赋值语句的条件。“过程赋值语句”左边的变量必须被定义成寄存器数据类型,右边变量可以是任意数据类型。beˉgin和end将多条过程赋值语句包围起来,组成一个顺序语句块,块内的语句按照排列顺序依次执行,最后一条语句执行完后,执行挂起,然后anways语句处于等待状态,等待下一个事件的发生。注意,当begin和end之间只有一条语句,且没有定义局部变量时,则关键词begin和end可以被省略。

上一篇:DC2857A 串行语句块

公网安备44030402000607

公网安备44030402000607