UPD65808GL-E05-NMU 传输延迟时间tpLH和rpHL

发布时间:2019/10/16 12:02:10 访问次数:1400

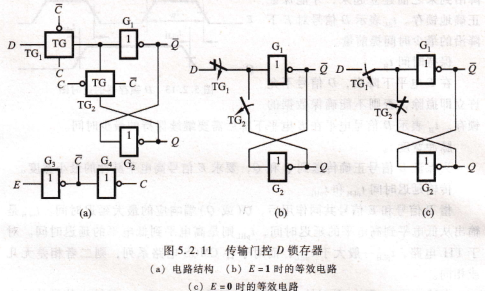

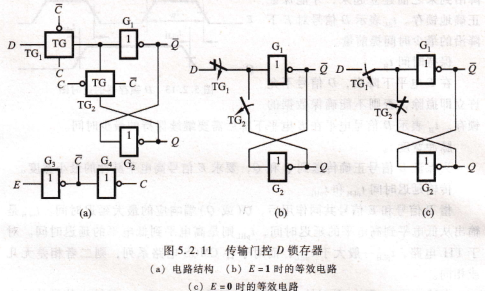

UPD65808GL-E05-NMU构成类似于图5.1.2所示的双稳态电路,如图5.2.11(c)所示。由于G1、G2输人端存在的分布电容对逻辑电平有暂短的保持作用,此时,电路将被锁定在E信号由1变0前瞬间D信号所确定的状态。读者可用表5,2.3来验证图5.2.11(a)所示电路的逻辑功能。由于逻辑功能完全相同,所以传输门控D锁存器的逻辑符号仍如图5.2.10(b)所示。

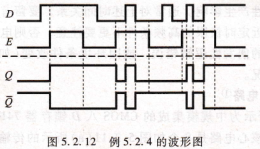

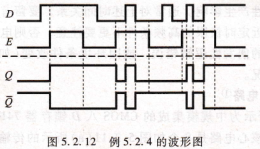

图5.2.11 传输门控D锁存器,电路结构 (b)E=1时的等效电路,E=0时的等效电路,例5,2,4 图5.2.11(a)所示电路的输入信号D、E的波形如图5.2.12虚线上边所示,画出O和口的输出波形。

解:根据图5.2.11(b)、(c),每当E=1时,o端波形跟随D端变化,当E跳变为0时,锁存器保持在跳变前瞬间的状态,可以画出Q和口波形,如图5.2.12虚线下边所示。

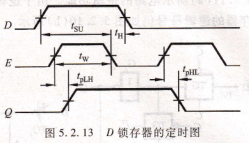

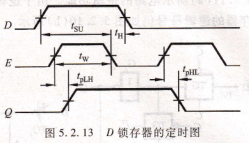

图5.2.12 例5.2.4的波形,3.D锁存器的动态特性定时图是表达时序电路动态特性的工具之一,它表达了电路动作过程中,对各输入信号的时间要求以及输出对输入信号的响应时间。图5.2.13所示是D锁存器的定时图,对图5,2.10(a)和图5.2.11(a)的电路都是适用的,只是具体参数值有所差异。下面对参数进行说明。

建立时间Jsu,数据信号D应在门控信号E下D降沿到来之前建立起来,才能保证正确地锁存。Jsu表示D信号对E下降沿的最少时间提前量。

保持时间tH

在E电平下降后,D信号不允许立即撤除,否则不能确保数据的锁存。莎Ⅱ表示D信号电平在E电平下降后需要继续保持的最少时间。

脉冲宽度tw

为保证D信号正确传送到Q和回,要求E信号高电平脉冲的最小宽度。

传输延迟时间tpLH和rpHL

指D信号和E信号共同作用后,0(或口)端响应的最大延迟时间。tpLH是输出从低电平到高电平的延迟时间,rpⅢ则是高电平到低电平的延迟时间。对于TTL电路,tpLH一般大于rpHL而对于各CMOS电路系列,则二者相差无几或相同。

UPD65808GL-E05-NMU构成类似于图5.1.2所示的双稳态电路,如图5.2.11(c)所示。由于G1、G2输人端存在的分布电容对逻辑电平有暂短的保持作用,此时,电路将被锁定在E信号由1变0前瞬间D信号所确定的状态。读者可用表5,2.3来验证图5.2.11(a)所示电路的逻辑功能。由于逻辑功能完全相同,所以传输门控D锁存器的逻辑符号仍如图5.2.10(b)所示。

图5.2.11 传输门控D锁存器,电路结构 (b)E=1时的等效电路,E=0时的等效电路,例5,2,4 图5.2.11(a)所示电路的输入信号D、E的波形如图5.2.12虚线上边所示,画出O和口的输出波形。

解:根据图5.2.11(b)、(c),每当E=1时,o端波形跟随D端变化,当E跳变为0时,锁存器保持在跳变前瞬间的状态,可以画出Q和口波形,如图5.2.12虚线下边所示。

图5.2.12 例5.2.4的波形,3.D锁存器的动态特性定时图是表达时序电路动态特性的工具之一,它表达了电路动作过程中,对各输入信号的时间要求以及输出对输入信号的响应时间。图5.2.13所示是D锁存器的定时图,对图5,2.10(a)和图5.2.11(a)的电路都是适用的,只是具体参数值有所差异。下面对参数进行说明。

建立时间Jsu,数据信号D应在门控信号E下D降沿到来之前建立起来,才能保证正确地锁存。Jsu表示D信号对E下降沿的最少时间提前量。

保持时间tH

在E电平下降后,D信号不允许立即撤除,否则不能确保数据的锁存。莎Ⅱ表示D信号电平在E电平下降后需要继续保持的最少时间。

脉冲宽度tw

为保证D信号正确传送到Q和回,要求E信号高电平脉冲的最小宽度。

传输延迟时间tpLH和rpHL

指D信号和E信号共同作用后,0(或口)端响应的最大延迟时间。tpLH是输出从低电平到高电平的延迟时间,rpⅢ则是高电平到低电平的延迟时间。对于TTL电路,tpLH一般大于rpHL而对于各CMOS电路系列,则二者相差无几或相同。

上一篇:AN983AL触发器的功能表

公网安备44030402000607

公网安备44030402000607