时钟电路的选择非常关键

发布时间:2019/7/29 21:12:25 访问次数:850

时钟电路

时钟电路的选择非常关键,因为它直接影响DDS的相位噪声水平。该电路要求输出最高频率为40MHz,考虑到滤波器的非理想性,一般输出频率由下面公式给出:LM3S8962-IQC50-A2

图3,5.3 频率合成器结构框图晶振选择频率为11。“吵MIIz高性能晶振,再利用AD9852内部时钟乘法器将外部参考时钟频率由11.Os呢MHz倍频到DDs系统时钟频率199.“56MlIz上。

低通滤波器

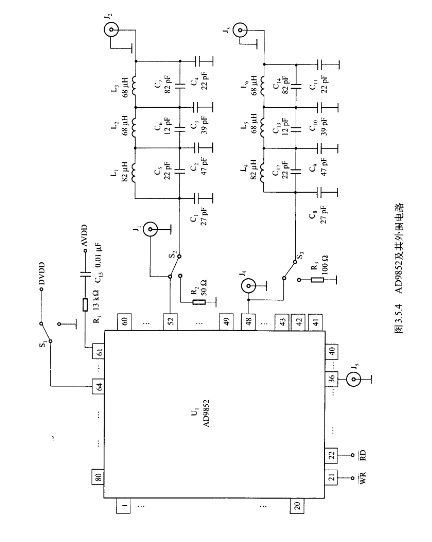

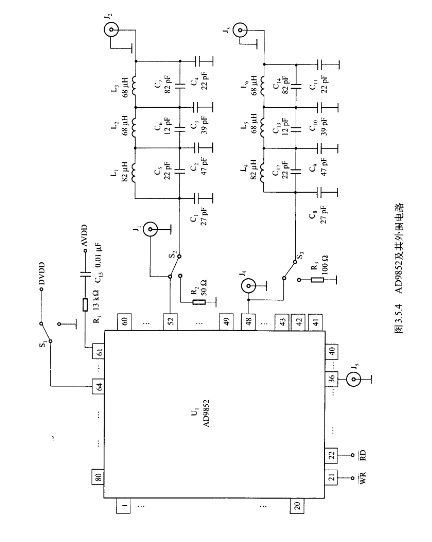

由于DDS芯片的输出具有大量的谐波分量及系统时钟干扰,低通滤波器能够较好地滤除杂波,平滑信号,所以为了得到所需频段内的信号,需要在DDS的输出端加一滤波器来实现。在实际滤波器中,用一个可实现的衰减特性来逼近理想特性,根据不同的逼近准则,采用不同的衰减特性来选择不同的频响滤波器。低通滤波器的频率响应主要有三种:巴特沃兹滤波器(最平坦响应滤波器),切比雪夫滤波器,椭圆函数滤波器。巴特沃兹低通滤波器的响应最为平坦,它的通带内没有波纹,在靠近0频处有最平坦通带,趋向阻带时衰减单调增大。它的缺点是从通带到阻带的过渡带最宽,对于带外干扰信号的衰减作用最弱。切比雪夫滤波器在通带内衰减在0值和一个上限值之间做等起伏变化,阻带内衰减单调增大。椭圆滤波器的衰减在通带和阻带内做等起伏变化。通

过三种滤波器在性能上的比较,椭圆函数滤波器的性能更好。其中,开关S1~S3为波形或低通滤波器选择开关。

时钟电路

时钟电路的选择非常关键,因为它直接影响DDS的相位噪声水平。该电路要求输出最高频率为40MHz,考虑到滤波器的非理想性,一般输出频率由下面公式给出:LM3S8962-IQC50-A2

图3,5.3 频率合成器结构框图晶振选择频率为11。“吵MIIz高性能晶振,再利用AD9852内部时钟乘法器将外部参考时钟频率由11.Os呢MHz倍频到DDs系统时钟频率199.“56MlIz上。

低通滤波器

由于DDS芯片的输出具有大量的谐波分量及系统时钟干扰,低通滤波器能够较好地滤除杂波,平滑信号,所以为了得到所需频段内的信号,需要在DDS的输出端加一滤波器来实现。在实际滤波器中,用一个可实现的衰减特性来逼近理想特性,根据不同的逼近准则,采用不同的衰减特性来选择不同的频响滤波器。低通滤波器的频率响应主要有三种:巴特沃兹滤波器(最平坦响应滤波器),切比雪夫滤波器,椭圆函数滤波器。巴特沃兹低通滤波器的响应最为平坦,它的通带内没有波纹,在靠近0频处有最平坦通带,趋向阻带时衰减单调增大。它的缺点是从通带到阻带的过渡带最宽,对于带外干扰信号的衰减作用最弱。切比雪夫滤波器在通带内衰减在0值和一个上限值之间做等起伏变化,阻带内衰减单调增大。椭圆滤波器的衰减在通带和阻带内做等起伏变化。通

过三种滤波器在性能上的比较,椭圆函数滤波器的性能更好。其中,开关S1~S3为波形或低通滤波器选择开关。

公网安备44030402000607

公网安备44030402000607