串扰测试

发布时间:2019/7/6 20:49:58 访问次数:734

串扰测试

近端串扰FAN301HLMY

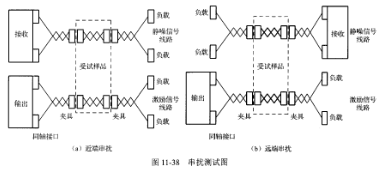

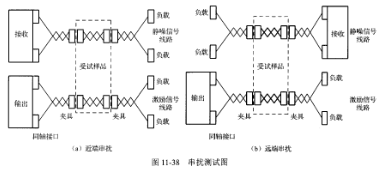

将高速差分连接器中的2对插合的差分接触件按图11-38(a)所示进行连接,未插合的差分接触对末端均需端接终端负载进行匹配。设置测试信号上升时间,由数字串行分析仪可读出接收通道的电压值,即为串扰电压。

图11-38 串扰测试图

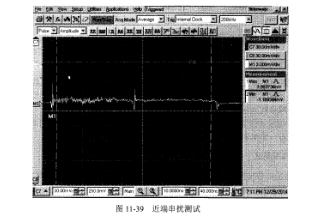

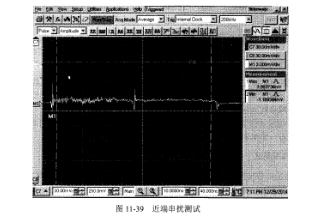

在对高速差分连接器的差分接触件进行近端串扰测试时,设置测试上升时间为2Sps(10%~⒛%),如图11-39所示,高速差分连接器的反射曲线中间出现一个干扰信号,测试接收信号的电压为5,”mV。

串扰测试

近端串扰FAN301HLMY

将高速差分连接器中的2对插合的差分接触件按图11-38(a)所示进行连接,未插合的差分接触对末端均需端接终端负载进行匹配。设置测试信号上升时间,由数字串行分析仪可读出接收通道的电压值,即为串扰电压。

图11-38 串扰测试图

在对高速差分连接器的差分接触件进行近端串扰测试时,设置测试上升时间为2Sps(10%~⒛%),如图11-39所示,高速差分连接器的反射曲线中间出现一个干扰信号,测试接收信号的电压为5,”mV。

热门点击

热门点击

- 间接寻址方式是指令给出存放操作数地址的存储单

- 射频连接器的检验依据主要有以下标准:

- 绝缘电阻

- PLC主机实现通信

- 脉冲上升时间与下降时间测试方法

- 频谱仪法测试步骤。

- RS-422接口

- 混合集成电路封装外壳

- 定义全局数据包(GD)

- 激光是指通过受激辐射而产生、放大的光

推荐技术资料

推荐技术资料

- 业余条件下PCM2702

- PGM2702采用SSOP28封装,引脚小而密,EP3... [详细]

公网安备44030402000607

公网安备44030402000607