构思顶层设计方框图

发布时间:2018/2/28 21:31:08 访问次数:1150

设计步骤

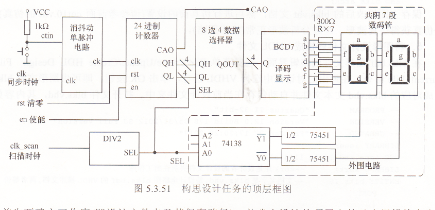

(1)构思顶层设计方框图。 OCM203构思的顶层方框图如图5.3,51所示,包括:消抖动单脉冲电路模块、24进制BCD计数器模块、数据选择器、BCD到七段码译码显示器模块、扫描时钟控制模块DIV2,这5个底层模块用一片CPLD(或FPGA)集中实现,是设计的重点,利用QLlartus II软件在计算机上完成设计并下载到CPLD(或FPGA)器件中;外围电路器件由按键、限流电阻、2只数码管、数码管阴极地址译码器(74138)、同相驱动器75451、连接用的飞线导线等组成。

图5351 构思设计任务的顶层框图

首先要建立工作库(即设计文件夹及其保存路径),并确定设计的顶层文件及底层模块名和设计输入方法,介绍如下。

设计文件夹cllt z bcd,路径D∶\cllt24bcd\,存放所有设计文件用。

顶层设计文件名:cdu24bcd7儿d叉原理图法)

底层设计文件名:①sin。oleJulse。bd※消抖动电路,原理图法)

②cnL24.vhd(z进制BCD计数器,文本法)

③mux廴4,vhd(8选4数据选择器,文本法)

④bm7,v・hd(BCD七段译码器,文本法)

⑤div2・・hd(扫描时钟控制器,文本法)

设计步骤

(1)构思顶层设计方框图。 OCM203构思的顶层方框图如图5.3,51所示,包括:消抖动单脉冲电路模块、24进制BCD计数器模块、数据选择器、BCD到七段码译码显示器模块、扫描时钟控制模块DIV2,这5个底层模块用一片CPLD(或FPGA)集中实现,是设计的重点,利用QLlartus II软件在计算机上完成设计并下载到CPLD(或FPGA)器件中;外围电路器件由按键、限流电阻、2只数码管、数码管阴极地址译码器(74138)、同相驱动器75451、连接用的飞线导线等组成。

图5351 构思设计任务的顶层框图

首先要建立工作库(即设计文件夹及其保存路径),并确定设计的顶层文件及底层模块名和设计输入方法,介绍如下。

设计文件夹cllt z bcd,路径D∶\cllt24bcd\,存放所有设计文件用。

顶层设计文件名:cdu24bcd7儿d叉原理图法)

底层设计文件名:①sin。oleJulse。bd※消抖动电路,原理图法)

②cnL24.vhd(z进制BCD计数器,文本法)

③mux廴4,vhd(8选4数据选择器,文本法)

④bm7,v・hd(BCD七段译码器,文本法)

⑤div2・・hd(扫描时钟控制器,文本法)

上一篇:Quartus Ⅱ的层次化设计

上一篇:设计底层模块。

公网安备44030402000607

公网安备44030402000607