计数及译码显示

发布时间:2016/12/17 19:29:27 访问次数:879

二-五-十进制加法计数器74I'S196构成电子秒表的计数单元,如图29.1中单元Ⅳ所示。H27U4G8F2ETR-BC其中,计数器74LS196(1)接成五进制形式,对频率为50Hz的时钟脉冲进行5分频,在输出端Q获取得周期为0.1s的矩形脉冲,作为计数器74IE196(2)的时钟输入,计数器74IE196(2)及74I'S196(3)接成8421码十进制形式,其输出端与实验设各上译码显示单元的相应输人端连接,可显示0,1~0,9s、1~9.9s。

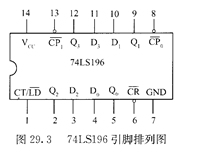

5.74LS196引脚排列及功能图29,3所示为74I冫S196的引脚排列,表29,l为其功能表。异步清除端CR为低电平时,可完成清除功能,与时钟脉冲CPO、CP1状态无关c清除功能完成后,应置高电平。计数/置数控制端CT/ID为低电平时,输出端α~G可预置成与数据输人端D3~D。相一致的状态,而 与币0、币1状态无关,预置后置高电平。计数时,恧、CT/LD置高电平,在∞。、币1下降沿时进行计数。

(1)十进制数(8421码):币1与G连接,计数脉冲由CPO输人。

(2)二-五混合进制计数:CPO与α连接,计数脉冲由CP1输人。

(3)2分频、5分频计数:CPO输人,在G得2分频输出;CP1输入,在Q1~电得5分频输出。

二-五-十进制加法计数器74I'S196构成电子秒表的计数单元,如图29.1中单元Ⅳ所示。H27U4G8F2ETR-BC其中,计数器74LS196(1)接成五进制形式,对频率为50Hz的时钟脉冲进行5分频,在输出端Q获取得周期为0.1s的矩形脉冲,作为计数器74IE196(2)的时钟输入,计数器74IE196(2)及74I'S196(3)接成8421码十进制形式,其输出端与实验设各上译码显示单元的相应输人端连接,可显示0,1~0,9s、1~9.9s。

5.74LS196引脚排列及功能图29,3所示为74I冫S196的引脚排列,表29,l为其功能表。异步清除端CR为低电平时,可完成清除功能,与时钟脉冲CPO、CP1状态无关c清除功能完成后,应置高电平。计数/置数控制端CT/ID为低电平时,输出端α~G可预置成与数据输人端D3~D。相一致的状态,而 与币0、币1状态无关,预置后置高电平。计数时,恧、CT/LD置高电平,在∞。、币1下降沿时进行计数。

(1)十进制数(8421码):币1与G连接,计数脉冲由CPO输人。

(2)二-五混合进制计数:CPO与α连接,计数脉冲由CP1输人。

(3)2分频、5分频计数:CPO输人,在G得2分频输出;CP1输入,在Q1~电得5分频输出。

上一篇:时钟发生器

上一篇:由于实验电路中使用的器件较多

公网安备44030402000607

公网安备44030402000607