SPI串行总线介绍

发布时间:2011/10/10 11:22:40 访问次数:1145

串行外设设备接口SPI( Serial Peripheral Interface)总线技术是Motorola金司推出的一种同步串行接口,Motorola公司生产的绝大多数MCU(微控制器)都配有SPI硬件接口,如68系列MCU。SPI用于CPU与各种外围器件进行全双工、同步串行通信。SPI可以同时发出和接收串行数据。它只需四条线就可以完成MCU与各种外围器件的通信,即串行时钟线(CSK)、主机输入/从机输出数据线(MISO)、主机输出/从机输入数据线(MOSI)、低电平有效从机选择线CS。

SPI接口主要应用在TTL移位寄存器、E2PROM、FLASH、实时时钟、LCD显示驱动器、A/D、D/A转换子系统、网络控制器或其他的MCU。

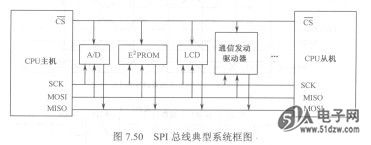

当SPI工作时,在移位寄存器中的数据逐位从输出引脚(MOSI)输出(高位在前),同时从输入引脚( MISO)接收的数据逐位移到移位寄存器(高位在前)。发送一个字节后,从另一个外围器件接收的字节数据进入移位寄存器中。主SPI的时钟信号(SCK)使传输同步。其典型系统框图如图7.50所示。 AD1100AR

SPI主要特点:

・可以同时发出和接收串行数据;

・可以当做主机或从机工作;

・提供频率可编程时钟;

・发送结束中断标志;

・写冲突保护;

・总线竞争保护。

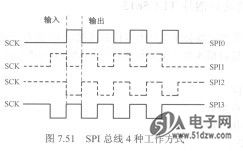

图7.51所示为SPI总线的4种工作方式,其中使用最为广泛的是SPIO和SPI3方式(实线表示)。

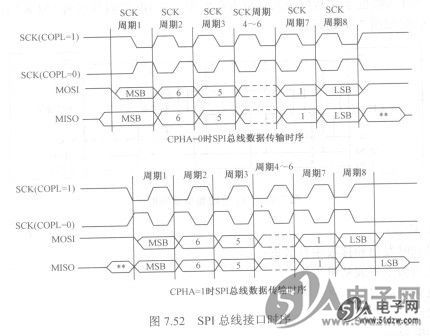

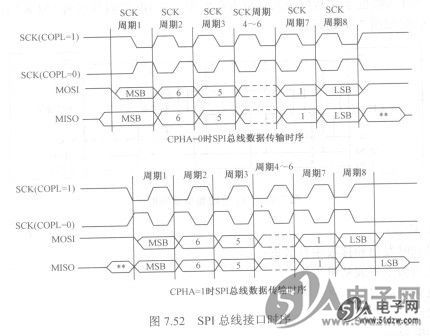

SPI模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性( CPOL)对传输协议没有重大的影响。如果CPOL-O,串行同步时钟的空闲状态为低电平;如果CPOL-1.串行同步时钟的空闲状态为高电平。时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。如果CPHA=O,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。SPI主模块和与之通信的外设间时钟相位和极性应该一致。SPI总线接口时序如图7.52所示。

SP1可工作在主模式或从模式下。在主模式,每一位数据的发送接收需要1次时钟作用,而在从模式下,每一位数据都是在接收到时钟信号之后才发送接收的。 AD136R950

串行外设设备接口SPI( Serial Peripheral Interface)总线技术是Motorola金司推出的一种同步串行接口,Motorola公司生产的绝大多数MCU(微控制器)都配有SPI硬件接口,如68系列MCU。SPI用于CPU与各种外围器件进行全双工、同步串行通信。SPI可以同时发出和接收串行数据。它只需四条线就可以完成MCU与各种外围器件的通信,即串行时钟线(CSK)、主机输入/从机输出数据线(MISO)、主机输出/从机输入数据线(MOSI)、低电平有效从机选择线CS。

SPI接口主要应用在TTL移位寄存器、E2PROM、FLASH、实时时钟、LCD显示驱动器、A/D、D/A转换子系统、网络控制器或其他的MCU。

当SPI工作时,在移位寄存器中的数据逐位从输出引脚(MOSI)输出(高位在前),同时从输入引脚( MISO)接收的数据逐位移到移位寄存器(高位在前)。发送一个字节后,从另一个外围器件接收的字节数据进入移位寄存器中。主SPI的时钟信号(SCK)使传输同步。其典型系统框图如图7.50所示。 AD1100AR

SPI主要特点:

・可以同时发出和接收串行数据;

・可以当做主机或从机工作;

・提供频率可编程时钟;

・发送结束中断标志;

・写冲突保护;

・总线竞争保护。

图7.51所示为SPI总线的4种工作方式,其中使用最为广泛的是SPIO和SPI3方式(实线表示)。

SPI模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性( CPOL)对传输协议没有重大的影响。如果CPOL-O,串行同步时钟的空闲状态为低电平;如果CPOL-1.串行同步时钟的空闲状态为高电平。时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。如果CPHA=O,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。SPI主模块和与之通信的外设间时钟相位和极性应该一致。SPI总线接口时序如图7.52所示。

SP1可工作在主模式或从模式下。在主模式,每一位数据的发送接收需要1次时钟作用,而在从模式下,每一位数据都是在接收到时钟信号之后才发送接收的。 AD136R950

上一篇:I2C总线模块之间的双线通信

上一篇:SPI总线接口器件TLC5615

热门点击

热门点击

- 耳机的结构特点

- A/D转换器的分类及简介

- 数字电路基础知识

- Proteus的主要功能和特点

- 调幅收音机组成方框图

- 三极管外形特征和电路符号识图信息

- 电阻器的图形符号及单位

- 功率放大电路的工作状态有几种?

- 二极管电路符号识图信息和基本工作原理

- 湿敏电阻简介

推荐技术资料

推荐技术资料

- FU-19推挽功放制作

- FU-19是国产大功率发射双四极功率电二管,EPL20... [详细]

公网安备44030402000607

公网安备44030402000607